Physical Design이란?

Physical Design이란 합성과정을 통해 Netlist 형태로 존재하는 회로를 실제 공정이 가능한 기하학적 구조(manufacturable geometries 또는 layout)으로 바꾸는 과정이라고 할 수 있습니다.

Physical Design의 전반적인 Flow는 다음의 4가지 단계를 따르게 됩니다.

Lab을 통해 Physical Design의 전반적인 flow를 배울 수 있었고, 제가 진행한 Lab에서의 Flow는 다음과 같습니다.

1. Design Import

2. FloorPlan & PowerPlan

3 .Placement

4. CTS(Clock Tree Synthesis)

5. Route

1. Design Import

Design import를 통해 합성된 netlist, I/O, block들을 읽어옵니다.

2. FloorPlan & PowerPlan

- FloorPlan

Design Import를 완료했다면, FloorPlan을 진행합니다.

FloorPlan이란, 주요 기능들을 하는 Block(IP block과 같은)을 칩 안에 배치하는 과정입니다. 이 FloorPlan을 어떻게 하느냐에 따라 칩의 성능이 좌우될 수 있습니다.

먼저 Power Ring을 배치할 공간을 확보하기 위해서 I/O와 I/O사이, I/O와 core 사이의 공간을 확보해줍니다.

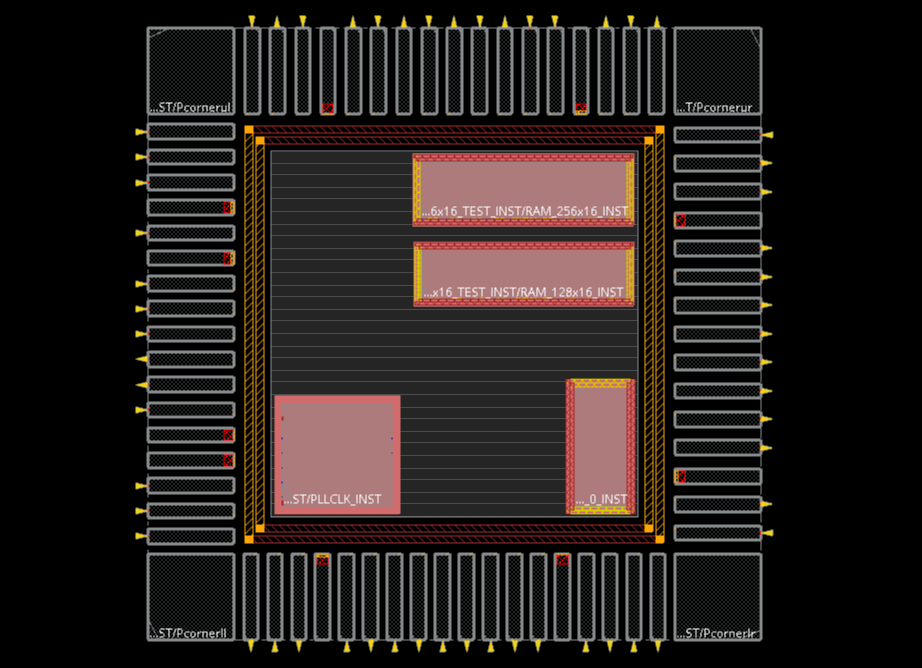

다음으로 실제 블록을 core에 배치하는 FloorPlan을 진행합니다. 아래의 그림은 FloorPlan이 완료된 모습입니다. 실제 칩에서는 이것보다 훨씬 많은 Block이 있기 때문에 과정이 더욱 복잡합니다.

- PowerPlan

이제 PowerPlan을 진행합니다.

PowerPlan이란 각 block과 추후에 배치될 standard cell에 전원을 공급하기 위해 VDD, VSS의 line을 배치해주는 작업을 의미합니다.

먼저 I/O와 core사이에 VDD, VSS ring을 둘러줍니다.

ring을 연결했다면, 이 ring과 I/O pad의 전원공급부가 연결되도록 합니다.

다음으로 추후 placement에서 배치될 standard cell에 전원을 공급해주기 위한 Follow pin을 배치해줍니다.

마지막으로 follow pin에서 ring을 통해 전원을 공급해 줄 수 있도록 stripe를 배치하여 연결합니다.

3. Placement

Placement 과정에서는 실제 netlist들을 이루는 standar cell을 배치해주는 작업을 수행합니다.

먼저 SCAN logic을 삽입하고 standard cell을 배치합니다. 이 작업은 명령어를 치게 되면 tool이 자동으로 진행합니다.

하지만 이때 배치된 cell들은 최적화가 되어있지 않은 상황이기 때문에 다음과 같이 setup time violation이나 max capacitance, max_transition, max_fanout과 같은 violation이 남아있습니다.

※ hold time이 표시되지 않는 이유 - 아직 CTS를 진행하지 않았기 때문에 clock들은 ideal state입니다. 따라서 hold time은 CTS를 진행한 이후 실제 clock이 배치되어 어느정도의 skew 차이가 있을 때 진행하게 됩니다.

따라서 이런 standard cell들을 Optimization하는 과정을 거치게 됩니다. 이를 PlaceOpt라고 합니다.

위의 그림처럼 setup time violation과 max_cap같은 violation들이 최적화를 통해 해결되었음을 확인할 수 있습니다.

4. Clock Tree Synthesis(CTS)

다음으로 Clock Tree Synthesis 진행합니다. CTS의 필요성과 역할은 다음과 같습니다.

- CTS에서는 clock과 clock 사이에 밸런스를 맞추고 clock 그룹간의 skew 차이를 최소화하는 역할을 수행합니다.

- clock은 디지털회로에서 무엇보다 중요한 역할을 하기 때문에, clock의 line들은 특별한 rule을 통해 보호해 줄 필요가 있습니다. 이를 Non-Default Routing Rules(NDR rules)라고 하며, clock에 noise가 생기는 것을 방지하기 위해 shielding이나 spacing같은 작업을 수행합니다.

아래는 CTS를 완료한 모습입니다.

자세한 layout의 캡쳐는 하지 못했지만 H-tree 방식의 clock tree를 사용하였고, 중요 clock들에 어느정도의 spacing과 VSS 를 통한 shielding을 진행하였습니다.

clock tree synthesis를 완료한 뒤에 다음과 같이 clock group, clock의 도착시간, skew 차이 등을 확인할 수 있었습니다.

이제 실제 clock이 배치되었기 때문에 hold time violation을 계산할 수 있습니다. 아래의 그림과 같이 많은 hold time violation이 발생하였습니다.

따라서 최적화 과정을 통해 이 violation을 잡아주어야 합니다. 이를 Post CTS optimization 이라고합니다.

CTS가 최적화되어 hold time violation이 잡힌것을 확인할 수 있었습니다.

또한 hold time violation을 잡기 위해, tool에서 어떤 cell을 사용했는지 log를 통해 확인할 수 있습니다.

5. Route

CTS이후 Route를 진행하게 됩니다.

위에서 진행한 route는 일종의 logical route로써, 실제 공정의 design rule을 만족하지 않은 route이고, 연결되는 선만 우선적으로 배치한 경우입니다. 예를 들어 같은 metal line끼리 cross하여 short되는 것과 같은 design rule을 만족하지 않은 경우가 있습니다. 따라서 Route 과정을 통해 이런 logica route를 실제 공정의 Design Rule을 만족하는 Physical Route로 바꿔줄 필요가 있습니다.

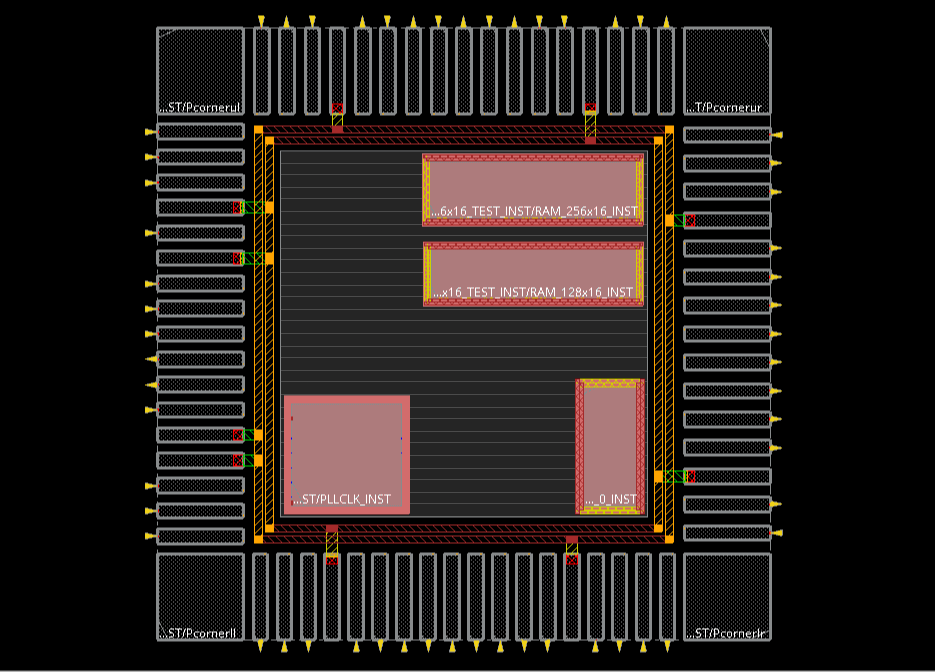

다음은 실제 Route를 완료한 모습입니다.

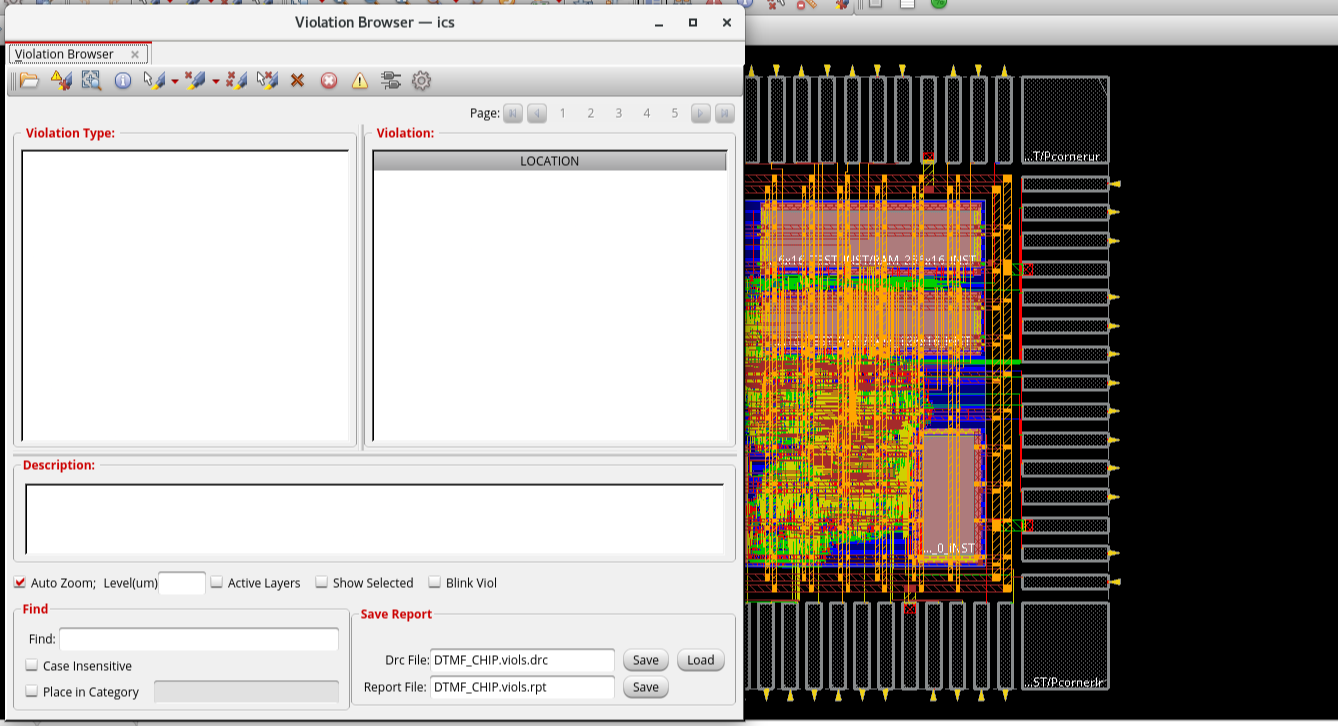

공정상의 Design Rule을 만족했음으로 DRC check를 하여 clean이 나타나는 것을 확인할 수 있습니다. 하지만 tool에서 가끔 DRC error가 뜨는 경우가 있습니다. 이때에는 사람이 직접 layout을 수정하거나 오류가 발생한 특정 line을 지우고 다시 Route를 진행하는 것으로 해결할 수 있습니다.

route가 완료되면 data path들이 design rule을 만족하기 위해 이리저리 돌아가야하는 경우가 생게 됩니다. 이로인해 아래의 그림처럼 여러 violation이 발생하게 됩니다.

따라서 이 violation을 잡아주기 위해 한번더 최적화하는 과정을 거치게 됩니다. 이를 PostRoute Optimization이라고 합니다.

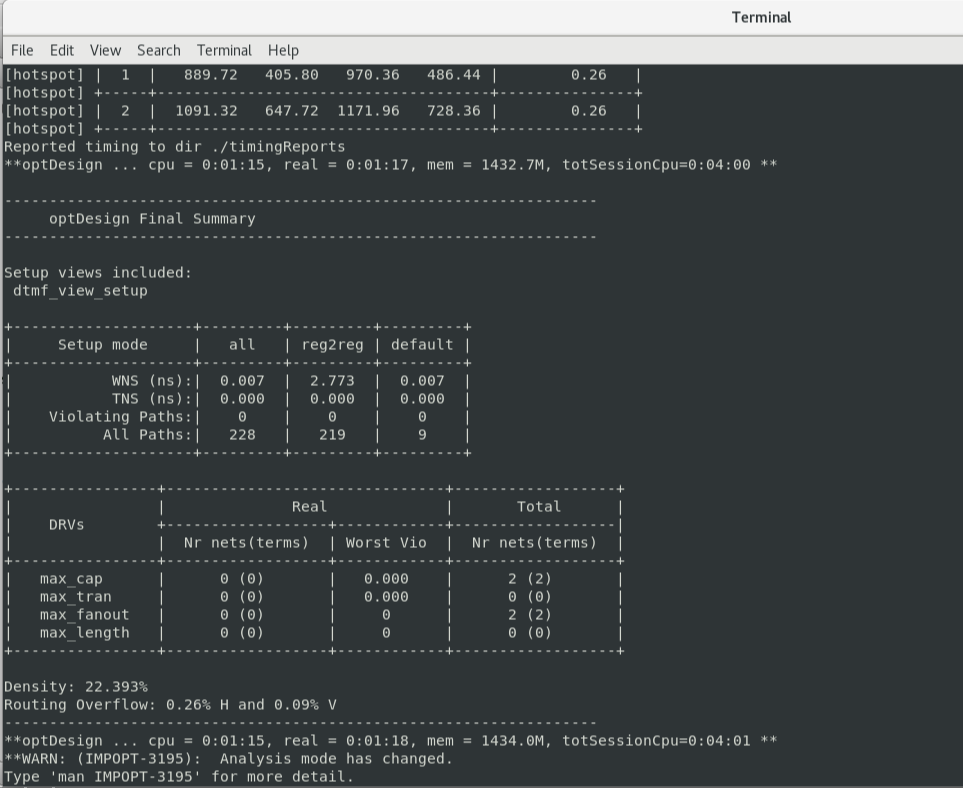

PostRoute optimization과정을 통해 physical route를 최적화하여 violation을 잡아준 모습을 확인할 수 있습니다.

이후 process variation을 조금이라도 줄이기 위해 filler를 채워주고, 구조가 무너지지 않도록 하는 Metal Fill 작업을 완료한 뒤, RC-Extraction을 진행하게 됩니다.

RC-Extraction에 대해서는 기회가 있다면 다뤄보도록 하겠습니다.