Overall ASIC Design Flow (3)

What is ASIC?

Application Specific Integrated Circuit(ASIC)은 특정한 사용을 위해 맞춤화된(customized) 집적회로이다.

ASIC의 제작과정은 크게 다음과 같다.

1. 디자인(Design)

2. 구현(Implementation)

3. 제작(Fabrication)

4. 패키지/테스트(Pakage/Test)

5. 양산(Mass-Production)

3. 제작(Fabrication)

제작 과정에서 다음과 같은 세부적인 과정으로 나뉘어질 수 있다.

3-1. Mask(마스크제작)

3-2. Fabrication Process(공정진행)

3-1. Mask (마스크제작)

마스크 제작 과정에서 구현 과정을 통해 그려준 layout을 공정 팀에 넘겨주기 위해서 GDSII 파일을 뽑아주게 된다. 이 GDSII 파일을 통해 공정쪽에서는 포토 마스크를 제작한다.

3-2. Fabrication Process(공정진행)

공정 진행 과정에서는 여러 공정들을 통해 실제 웨이퍼 위에 여러개의 칩을 찍어낸다.

https://www.youtube.com/watch?v=gld0IHfbyF8&t=111s

4. 패키징/테스트(Packaging/Test)

패키징/테스트 과정에서 다음과 같은 순서로 패키징을 진행한다.

1. 웨이퍼 절단 - 웨이퍼에 형성된 칩들을 절단하는 과정이다. 이때 웨이퍼 상에 형성되어 있는 칩을 die라고 한다. 좀 더 자세한 내용은 https://news.skhynix.co.kr/post/net-die-semiconductor 에서 확인할 수 있다.

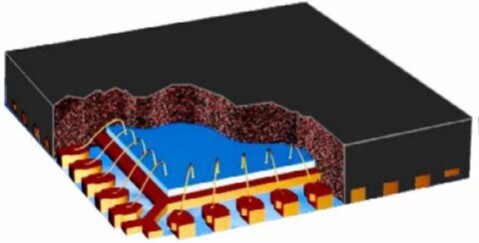

2. Wire bonding - 웨이퍼에서 잘라낸 칩을 리드프레임에 옮기고 칩이 외부세계와 전기적 신호를 주고받기 위하여 칩과 리드프레임간의 wire를 연결해주는 과정이다.

3. Molding - EMC(Epoxy Molding Compound)에 고온을 가하여 젤리 상태로 만든 후, 원하는 형태의 틀에 넣어 감싸주는 공정이다.

4. Ball attach - 칩에 ball을 붙이는 과정이다. 칩은 단독으로 존재하는 경우는 거의 없고, 대부분 PCB 기판 위에서 동작하게 된다. 이때 PCB 기판위의 Ball Grid Array(BGA)에 칩을 붙이기 위해 칩에도 ball을 붙여주어야 한다.

최근에는 이런 단순한 Lead Frame Package 방식이 아닌, 공정의 집적화 미세화에 따른 PCB기반의 Package 방식(PBGA, CSP LGA FCBGA, ...), Wafer Level Package방식 등과 같은 다양한 패키지 방식이 존재한다.

5. Test - 실제 만들어진 칩이 정상적으로 동작하는지 Test하는 과정이다.

5. 양산(Mass-Production)

모든 과정들이 정상적으로 끝났다면, 마지막으로 양산 과정을 통해 칩을 대량으로 찍어낸다. 이 때에도 품질검증, 불량검증 등 여러과정들이 들어가게 된다.