64bit Sram Design (3) - Circuit Topology & Schematic Design

64bit sram design 프로젝트에서 저희 팀이 정한 회로의 구조와 schematic은 다음과 같습니다.

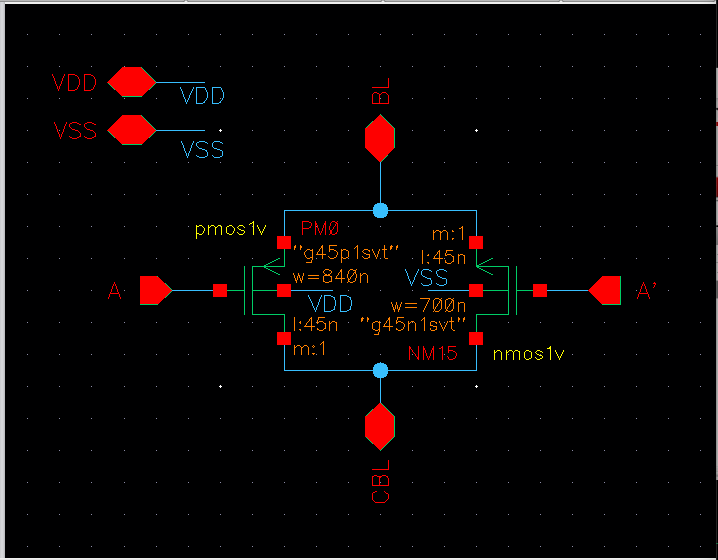

1. Sram cell

sram cell은 6T sram을 사용하였습니다.

6T sram을 사용한 이유는 다음과 같습니다.

- 디자인이 간단하다.

- 6개의 트랜지스터를 사용하여 8T sram 보다 면적이 작다.

- 8T sram 보다 더 적은 파워를 소모한다.

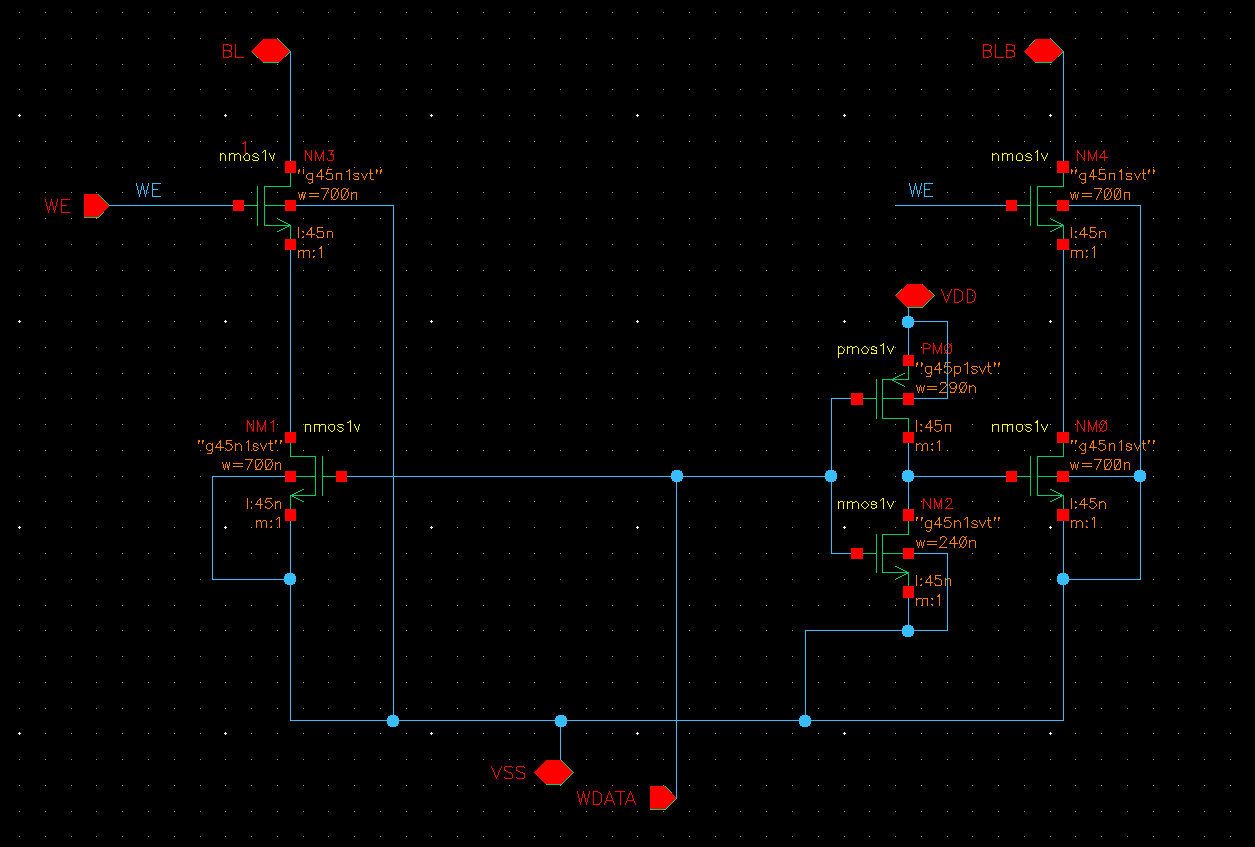

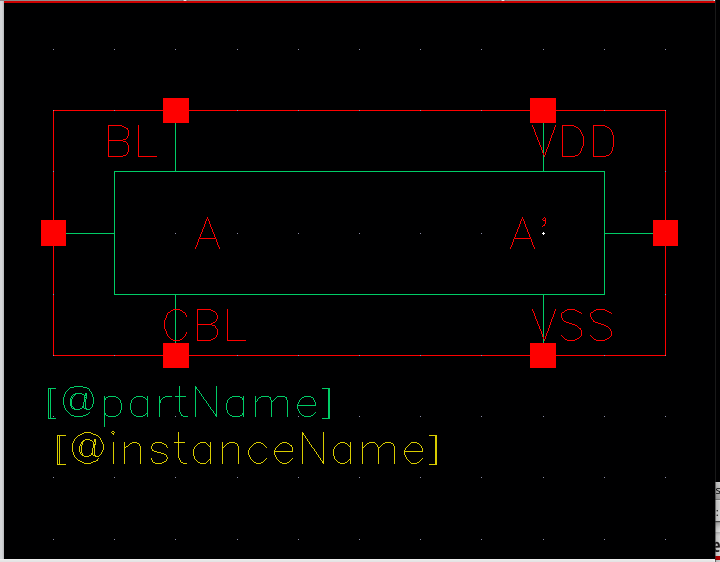

6T sram cell의 schematic과 symbol은 다음과 같습니다.

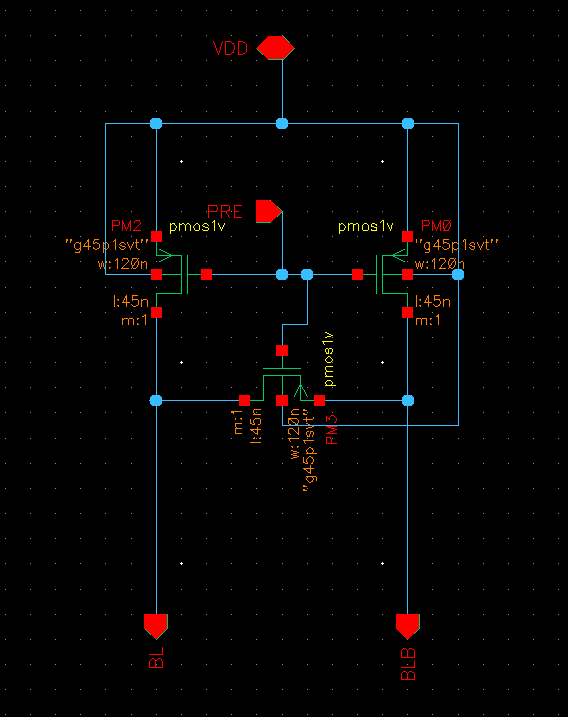

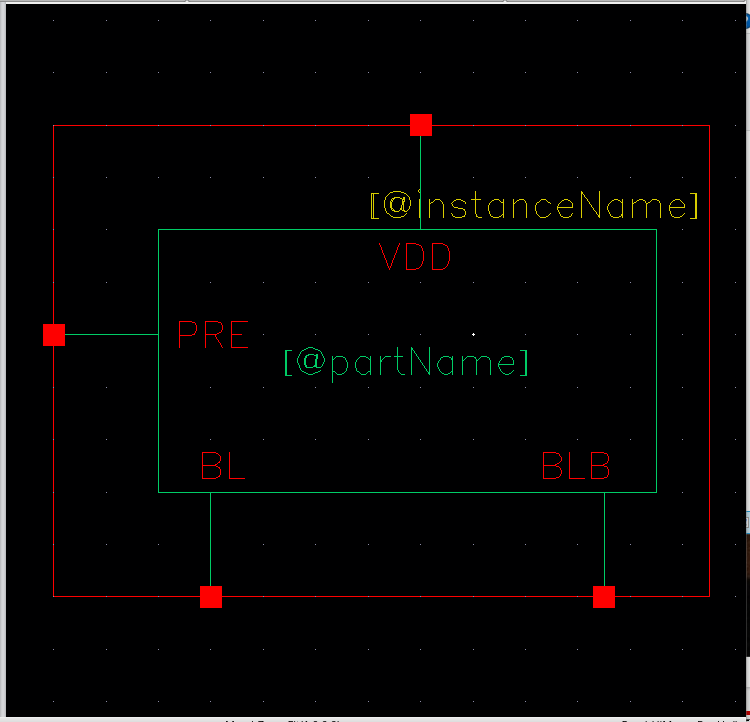

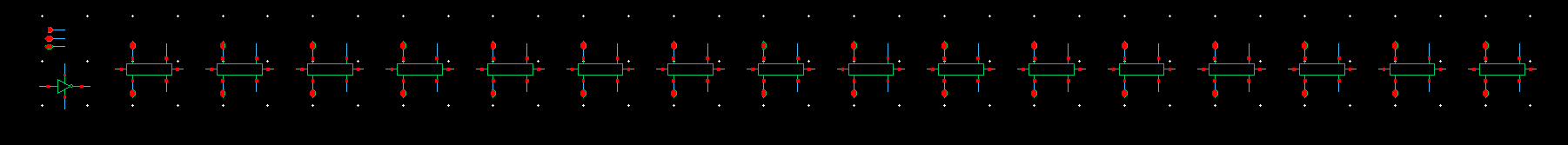

2. Precharge circuit

Precharge circuit은 pmos를 사용하였습니다. 또한 BL, BLB line을 연결하는 pmos를 사용하는 구조를 선택했습니다.

Precharge circuit에서 pmos를 사용한 이유는 다음과 같습니다.

pmos는 High 전압을 더 잘 전달할 수 있기 때문에 BL, BLB line을 VDD까지 채워줄 수 있습니다.

nmos를 사용할 경우 BL, BLB line이 VDD – Vth 까지만 charge 됩니다.

BL과 BLB line을 VDD로 precharge 시켜주는 이유는 sram cell의 access transistor를 nmos를 사용하였기 때문입니다.

Precharge circuit에서 BL, BLB를 연결하는 pmos를 사용한 이유는 다음과 같습니다.

BL와 BLB를 연결하는 pmos를 사용할 경우 BL와 BLB line의 전압을 같게 만들어 줄 수 있습니다.

BL와 BLB line의 전압을 같게 만들어 줄 경우, read 동작 시 sense amp의 동작에서 기존에 있던 값들을 한번 초기화시켜 준 후 새로운 값을 읽어들일 수 있기 때문입니다.(memory effect의 최소화)

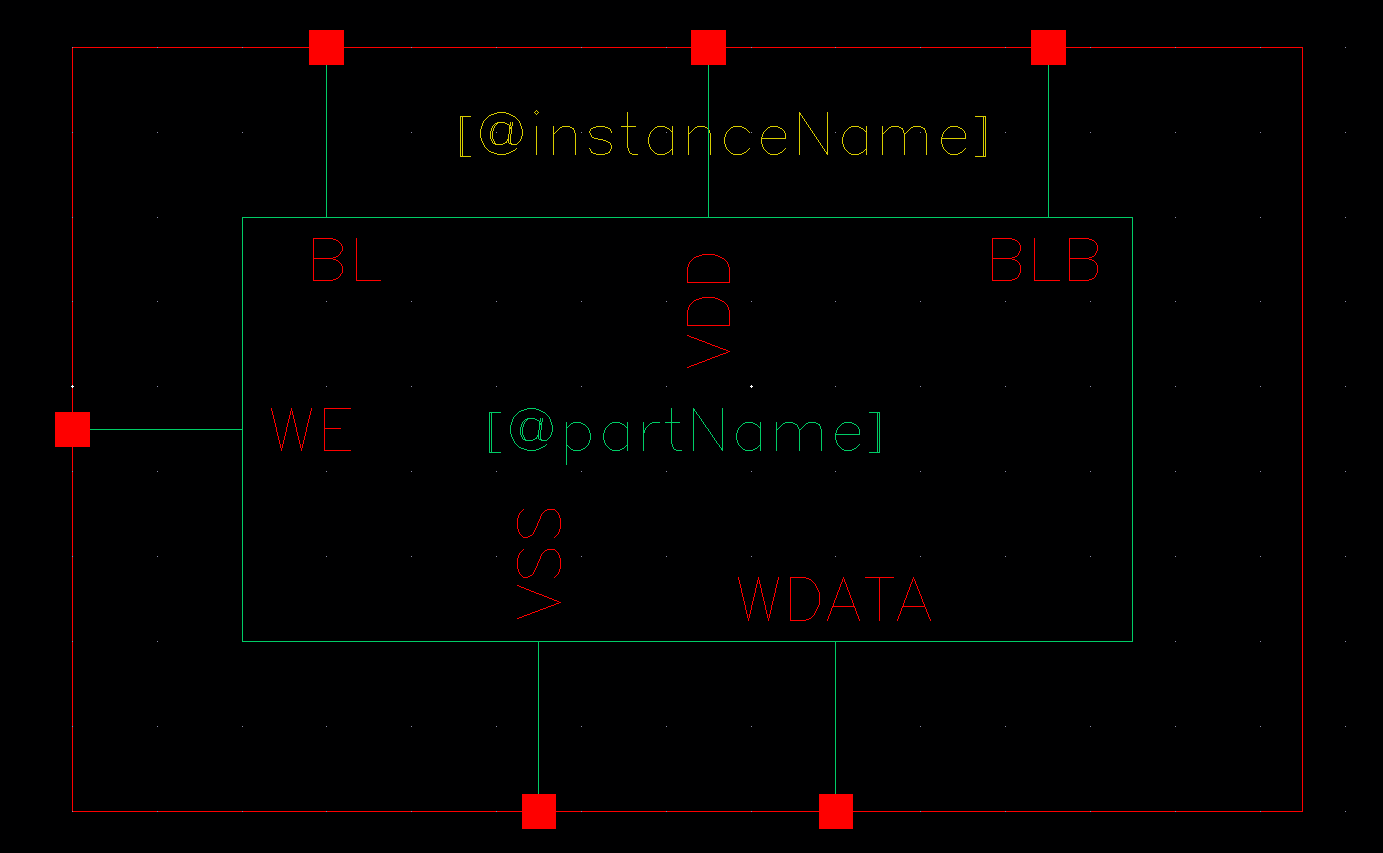

precharge circuit의 schematic과 symbol은 다음과 같습니다.

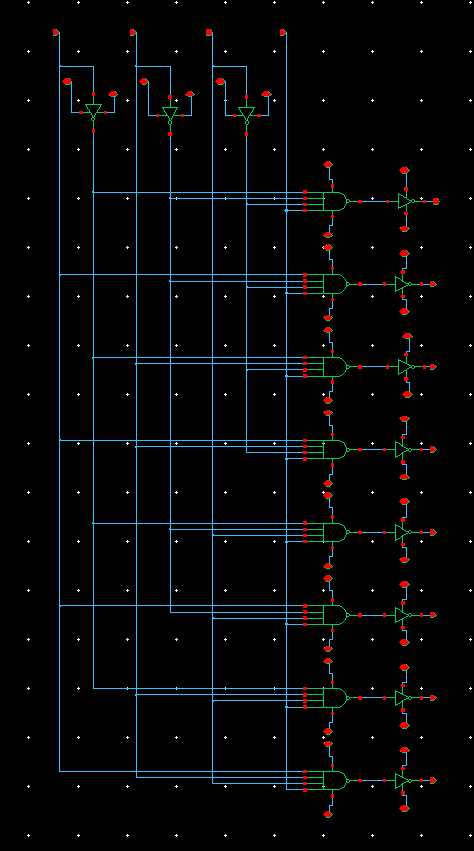

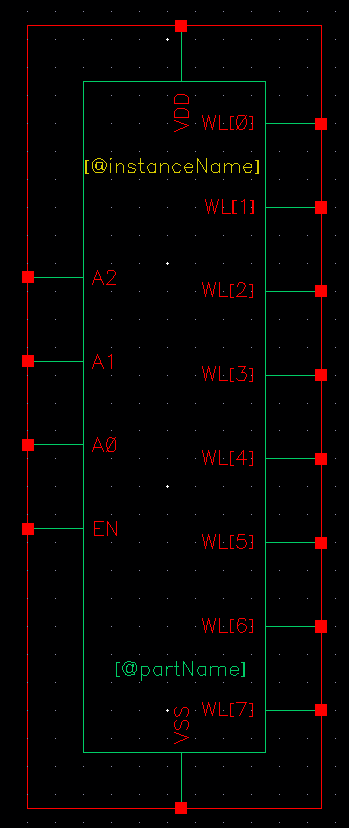

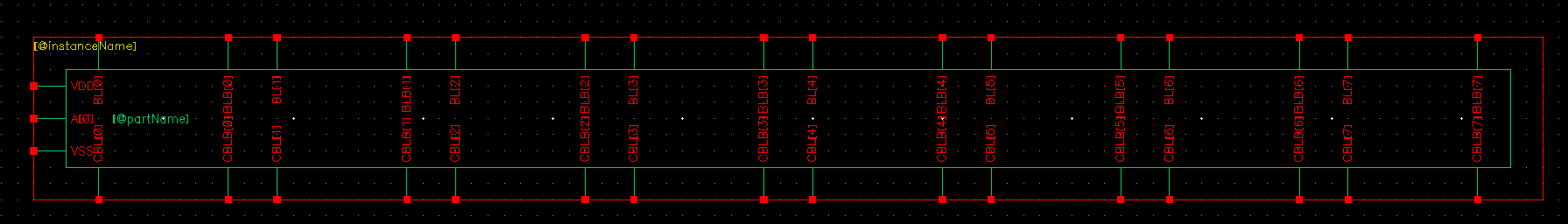

3. Row decoder

Row decoder는 mux구조를 사용하였으며, EN 신호를 따로 두어 사용하였습니다.

EN 신호를 사용한 이유는 다음과 같습니다.

EN(Enable) 신호를 사용하지 않고 row decoder를 구성할 경우 8개의 WL[X]중 무조건 1개의 WL[X]는 켜져있게 되고, 이는 sram cell의 의도치 않은 쓰기 혹은 읽기 동작을 유발할 수 있습니다. 또한 파워 소모면에서도 손해를 입게됩니다.

row decoder의 schematic과 symbol은 다음과 같습니다.

4. Column decoder

Column decoder는 transmisson gate로 구성하였습니다.

Column decoder를 transmisson gate로 구성한 이유는 다음과 같습니다.

nmos나 pmos만을 사용하여 pass transistor logic을 사용할 경우 1이나 0의 신호를 전달하는 것에 대해 손해를 보게 됩니다. 따라서 1과 0 신호를 모두 잘 전달해 주기 위해서 transmisson gate로 column decoder를 구성하였습니다.

column decoder의 schematic과 symbol은 다음과 같습니다.

5. Sense amplifier

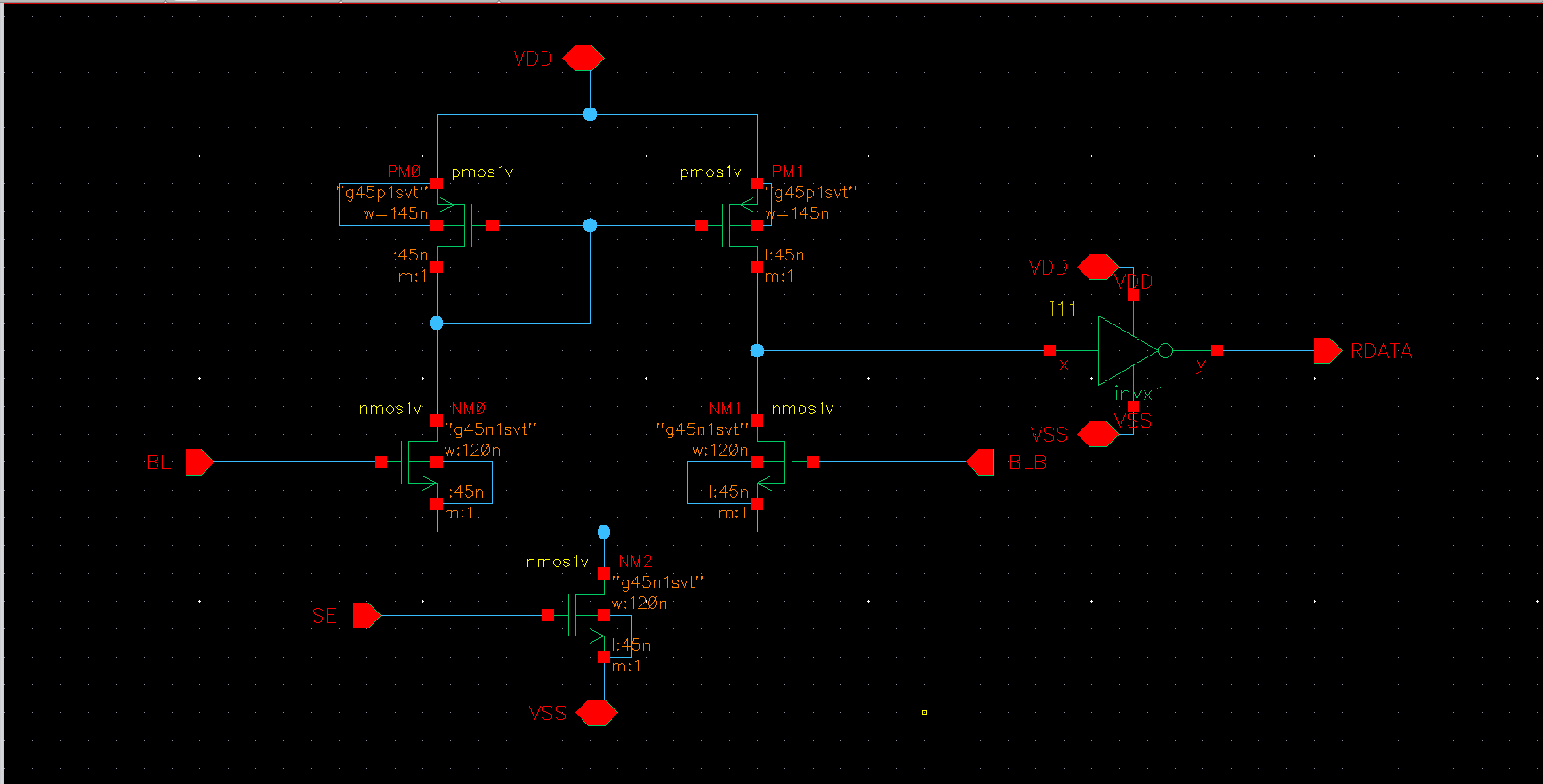

Sense amplifier는 current mirror type voltage sense amplifier를 사용하였습니다.

Sense amplifier를 current mirror type voltage sense amplifier로 구성한 이유는 다음과 같습니다.

- 회로의 구조가 상대적으로 간단합니다. 그래서 상대적으로 쉽게 회로를 해석할 수 있습니다.

- 입력과 출력이 분리되어 있습니다. 따라서 별도로 신호를 처리하는 과정을 거칠 필요가 없이 인버터를 사용하여 신호를 refresh 시키고 RDATA를 뽑아낼 수 있습니다.

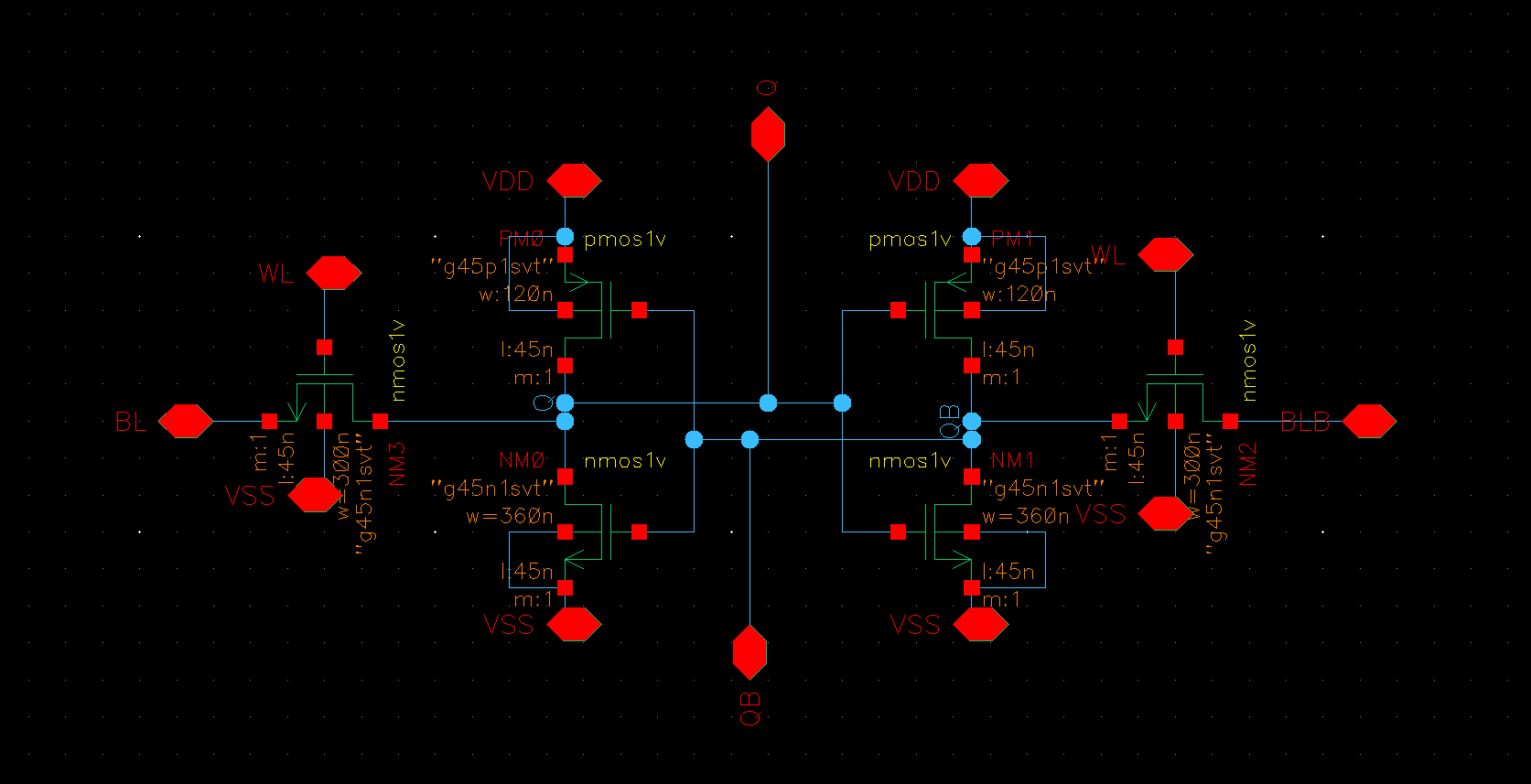

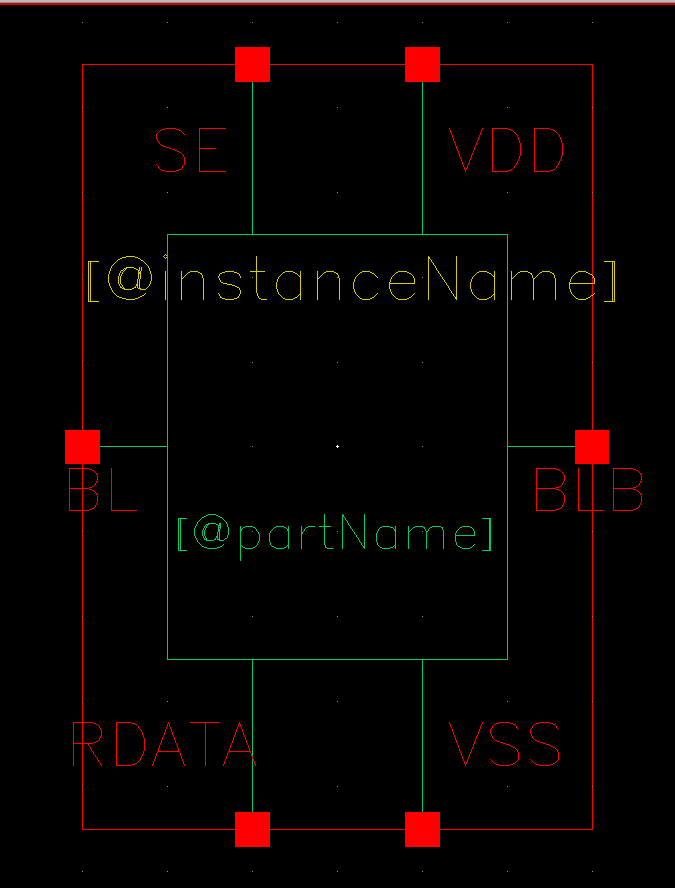

sense amplifier의 schematic과 symbol은 다음과 같습니다.

6. Write driver

Write driver는 WDATA가 1이되면 BL line이 0이 되고 WDATA가 0이되면 BLB line이 1이 되도록하는 동작을 수행합니다.(원하는 data를 BL, BLB line에 거꾸로 쓰게 됩니다.)

Write driver에서 거꾸로 쓰는 동작을 하도록 회로를 구성한 이유는 다음과 같습니다.

Sense amplifier에서 RDATA를 뽑을 때, inverter를 통해서 data를 거꾸로 뽑아내주기 때문에 write driver에서 sram cell에 data를 쓸 때 반대로 값을 써주어야 합니다.

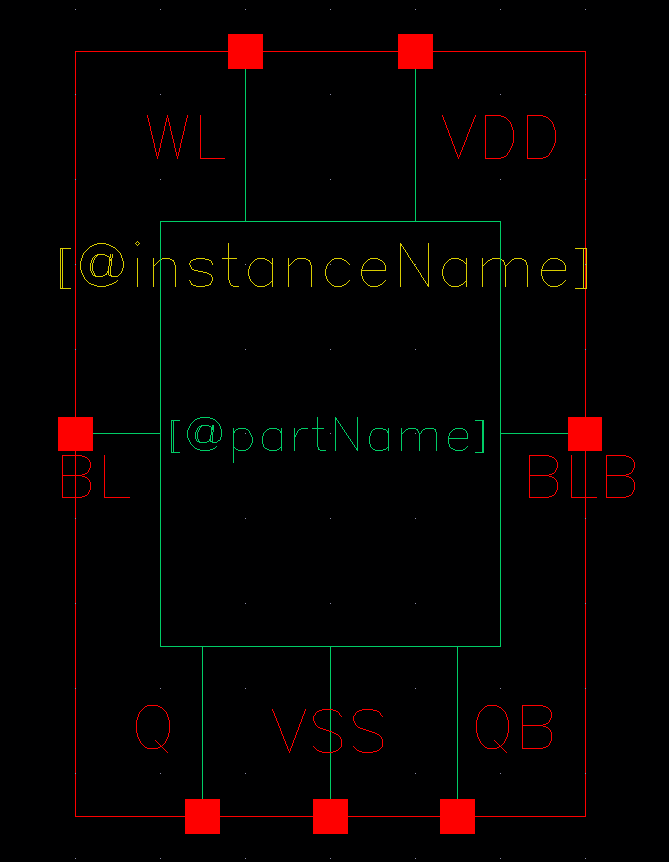

write driver의 schematic과 symbol은 다음과 같습니다.