64bit Sram Design (4) - Transistor Sizing

64bit sram design 프로젝트에서 각각의 sub-block의 transistor size와 그렇게 결정한 이유는 다음과 같습니다.

1. Sram cell

6T sram cell의 transistor size를 access transistor : 300nm, nmos : 360nm, pmos : 300nm로 결정하였습니다.

6T sram cell의 transistor size를 위와 같이 결정한 이유는 다음과 같습니다.

먼저 nmos의 사이즈인 360nm는 프로젝트에서 가이드라인으로 제공되었습니다. 이후 pmos와 access transistor의 size를 결정하기 위해 다음 논문의 Graphical Tech를 진행하였습니다.

Static-Noise Margin Analysis of MOS SRAM Cells - EVERT SEEVINCK, FRANS J. LIST, AND JAN LOHSTROH

https://www.youtube.com/watch?v=ltFrkpAEc0M&list=PLRrj_SkTRySRPq6r5w1zukxL5EEtnMZAh&index=3에 자세한 설명이 되어있습니다.

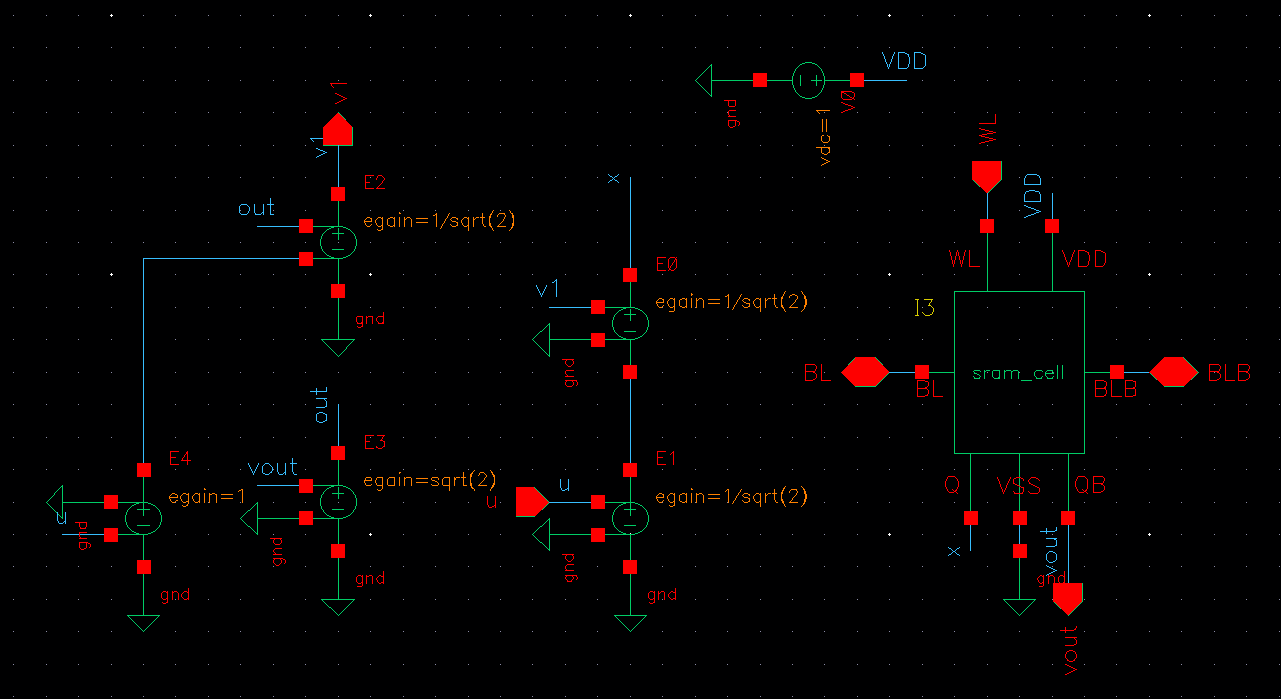

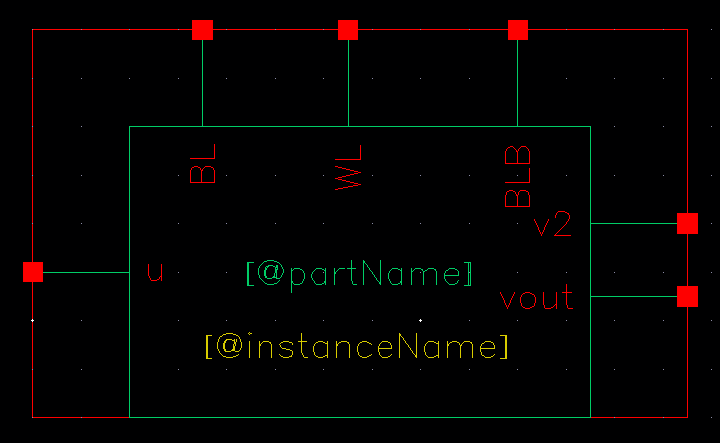

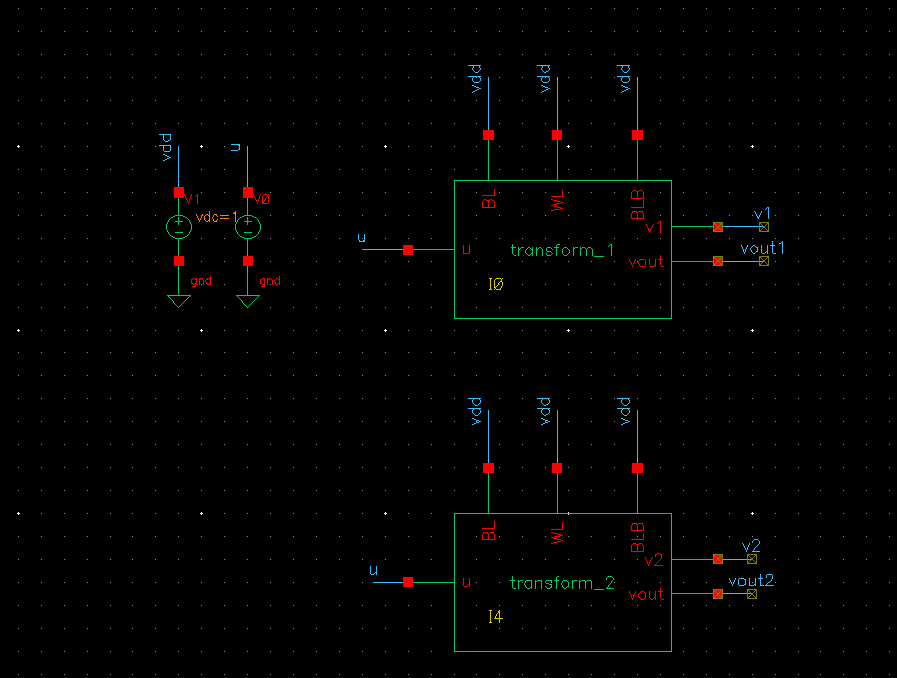

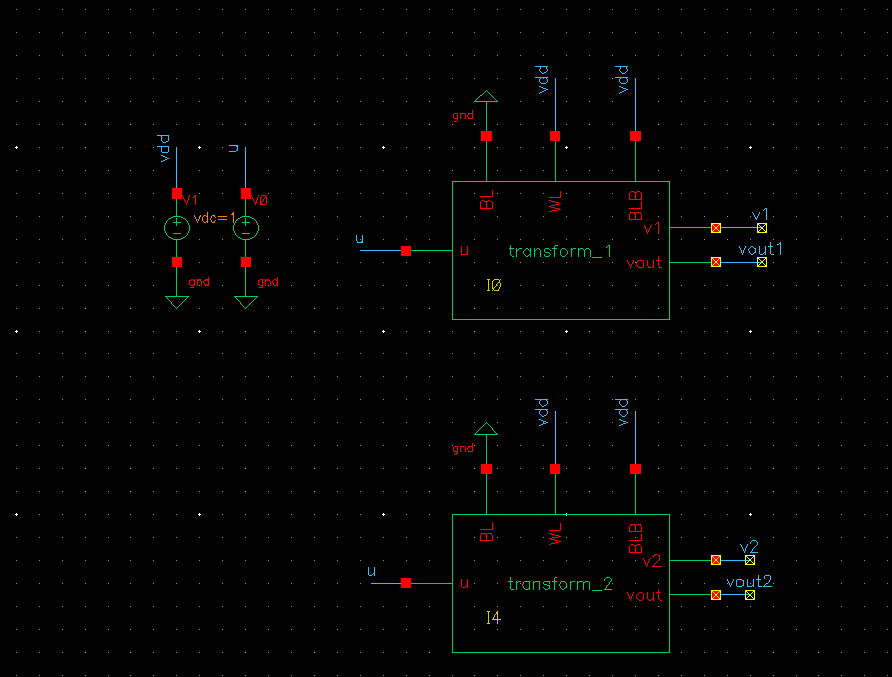

Graphical Tech를 위한 transform 회로의 schematic과 symbol은 다음과 같습니다.

transform1

transform2

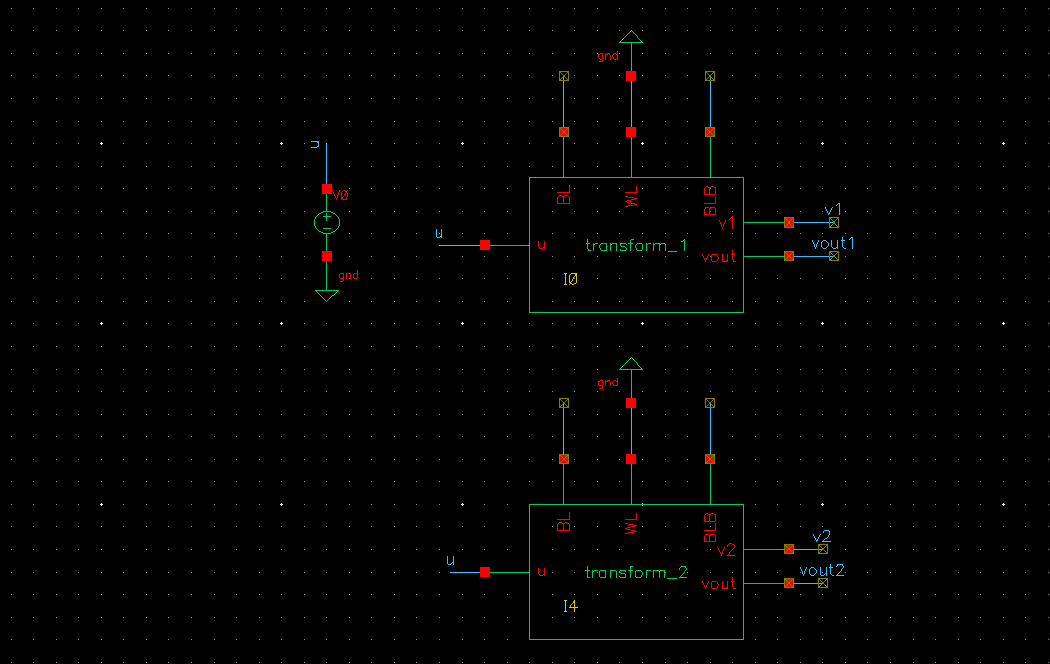

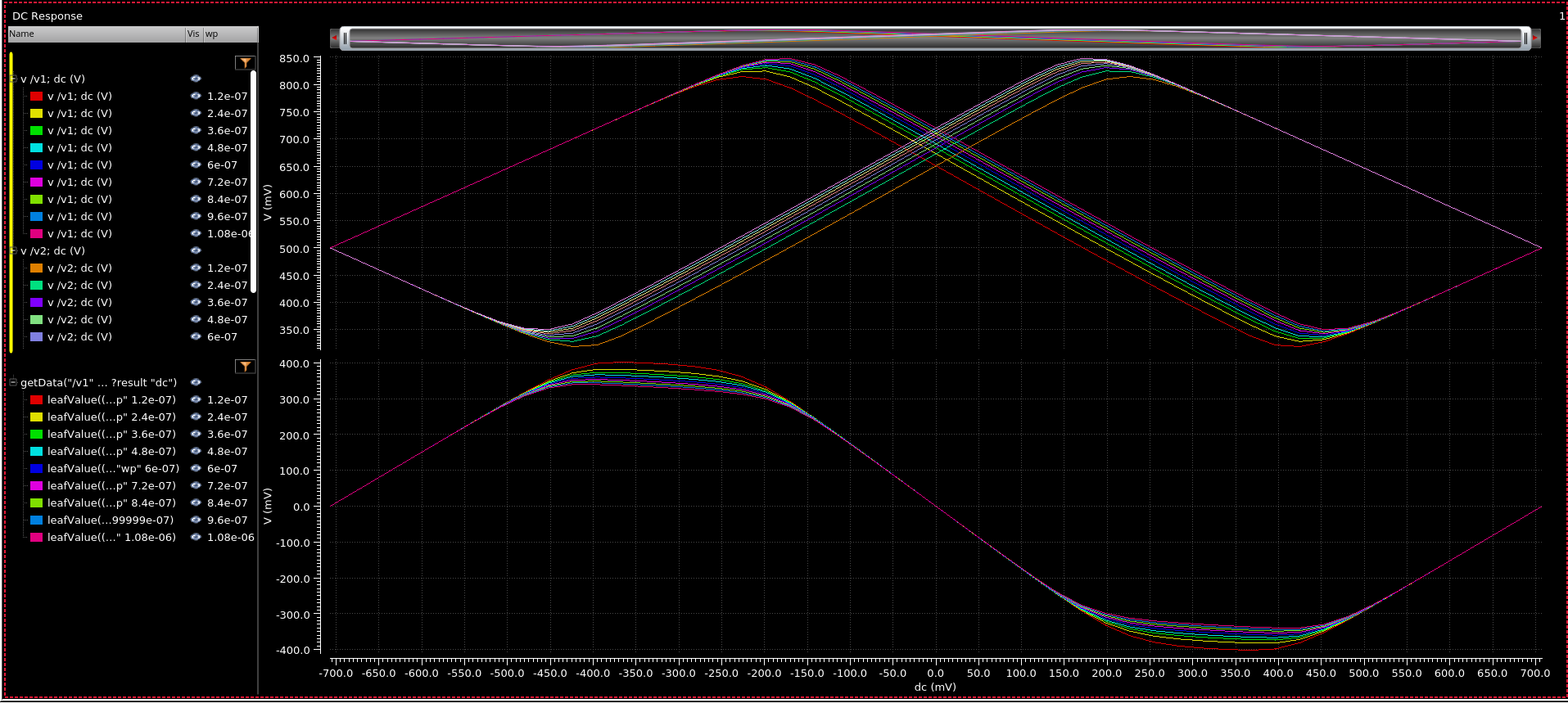

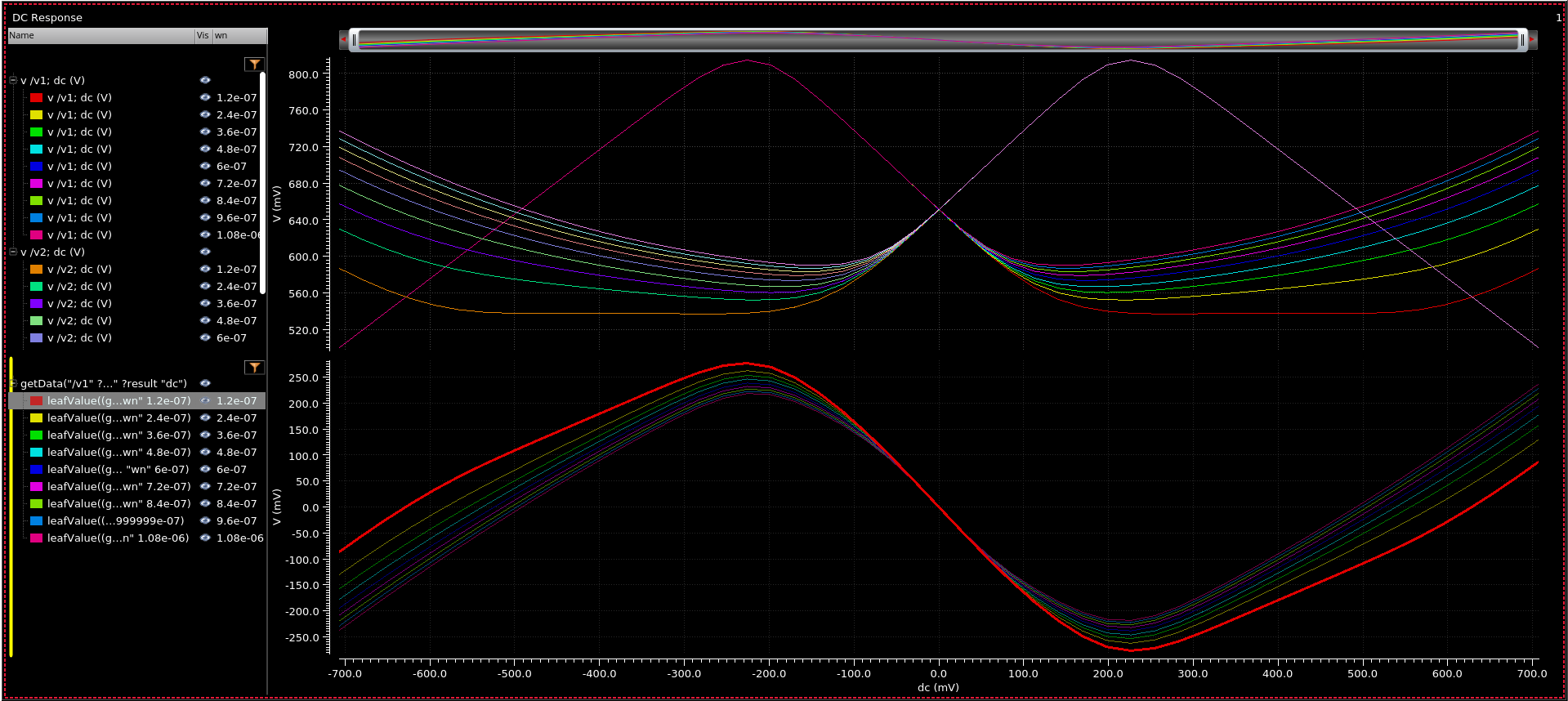

pmos의 size를 결정하기 위해서, SNM(Static Noise Margin)이 최대가 되는 지점을 구하기 위한 Testbench for SNM의 schematic과 waveform은 다음과 같습니다.

waveform에서 pmos의 사이즈가 120nm일 때 SNM이 최대가 됨을 확인했습니다. 따라서 pmos의 사이즈는 120nm로 결정하였습니다.

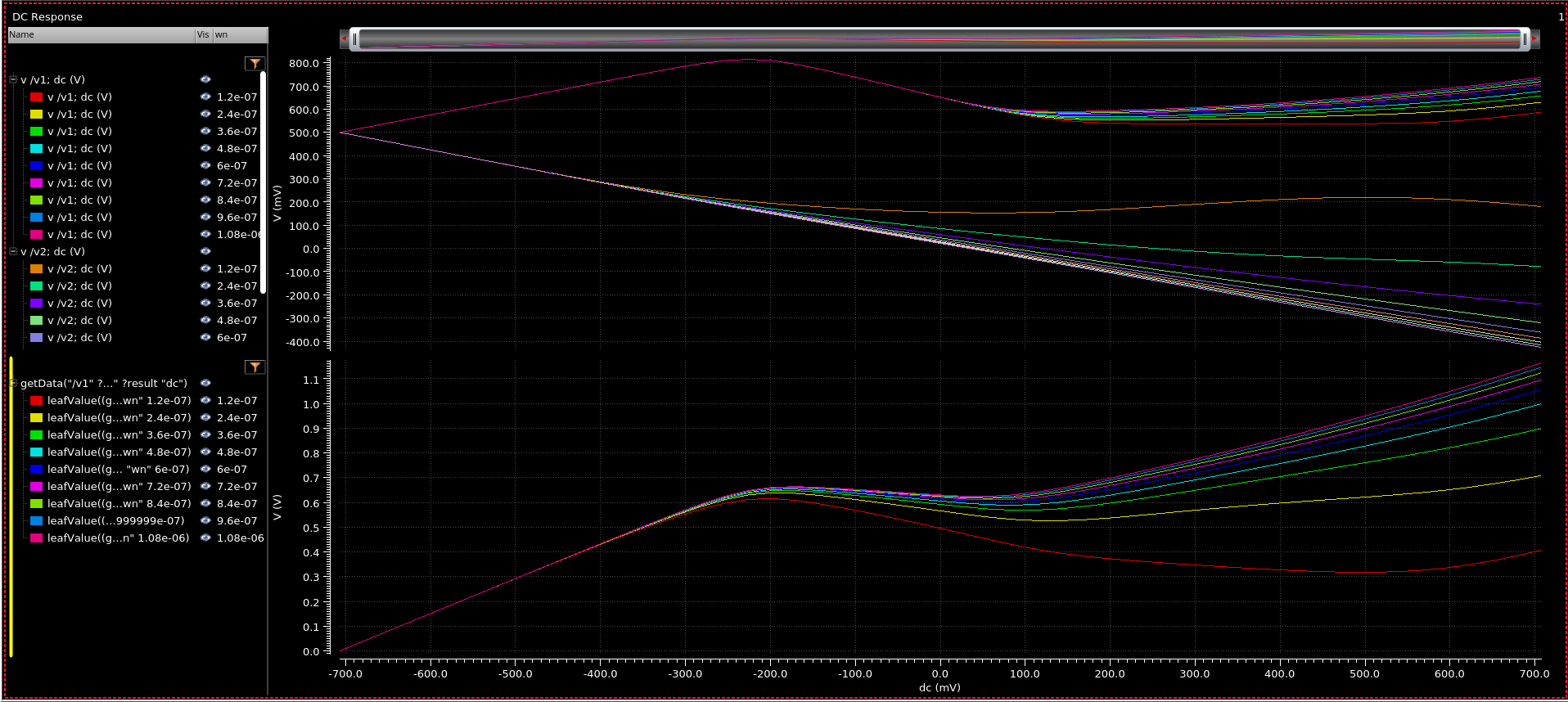

access transistor의 size를 결정하기 위해서, RNM(Read Noise Margin)이 최대가 되는 지점을 구하기 위한 Testbench for RNM과 waveform은 다음과 같습니다.

access transistor의 사이즈가 120nm일 때 RNM이 최대가 됨을 확인할 수 있었습니다. 즉, RNM은 access transistor의 사이즈가 작으면 작을수록 더 좋아짐을 알 수 있었습니다.

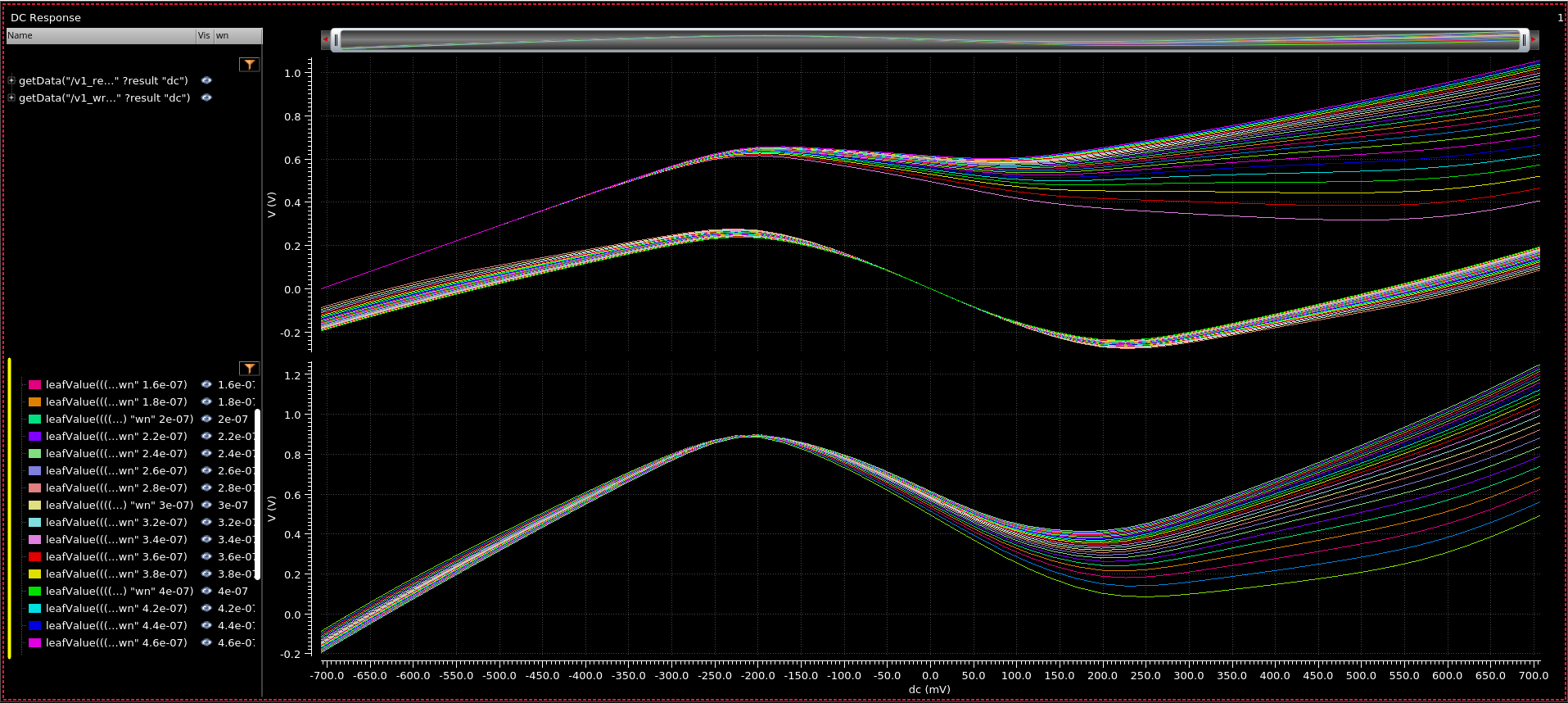

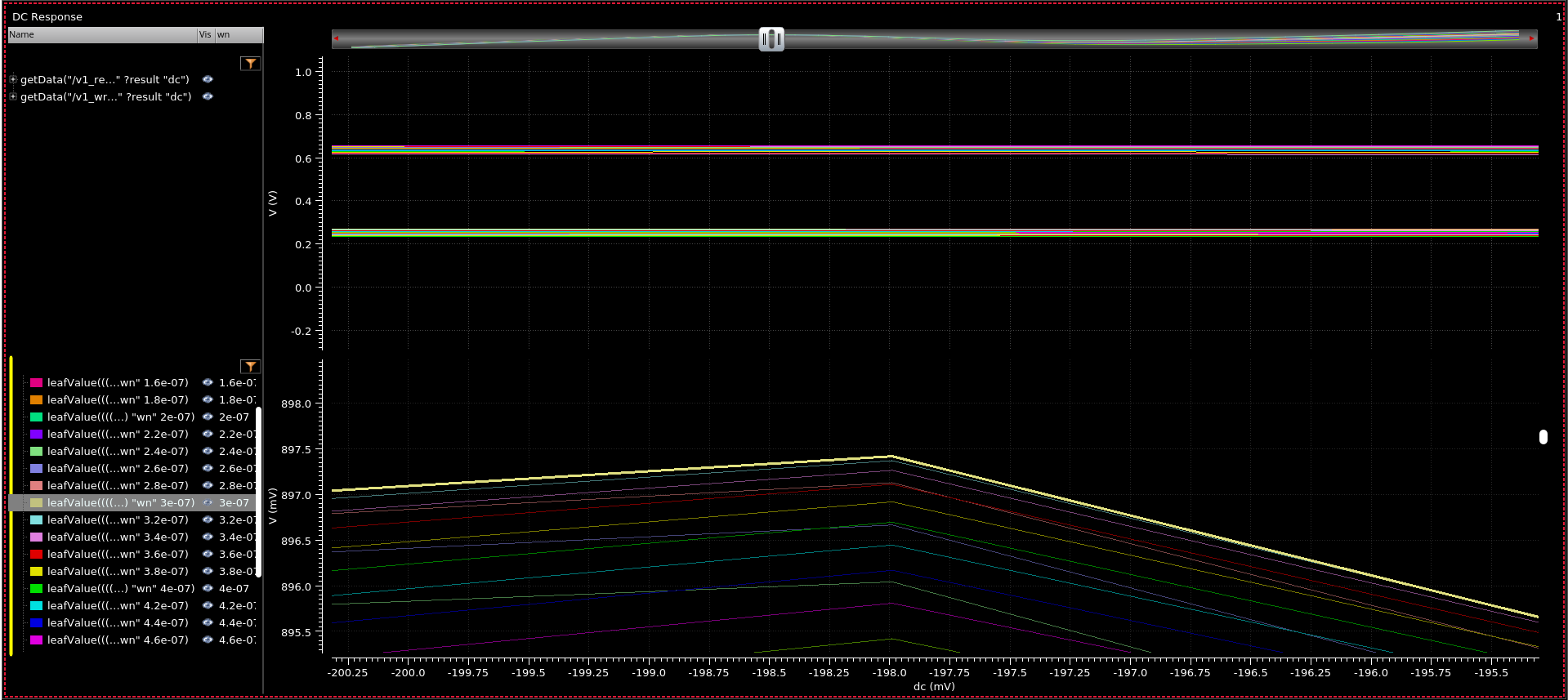

access transistor의 size를 결정하기 위해서, WNM(Write Noise Margin)이 최대가 되는 지점을 구하기 위한 Testbench for WNM과 waveform은 다음과 같습니다.

access transistor의 사이즈가 1080nm일 때 WNM이 최대가 됨을 확인할 수 있었습니다. 즉, WNM은 access transistor의 size가 크면 클수록 더 좋아짐을 알 수 있었습니다.

하나의 그래프는 크기가 작으면 커지고(RNM), 다른 그래프는 크기가 크면 커지게 됩니다(WNM). 따라서 RNM과 WNM에 대해 Max(RNM+WNM)가 되는 지점을 찾기 위해 두 그래프를 더한 결과 다음과 같은 waveform을 얻을 수 있었습니다.

access transistor가 300nm에서 Max(RNM+WNM)이 나옴을 확인할 수 있었습니다. 따라서 access transistor의 사이즈는 300nm로 결정하였습니다.

2. Precharge circuit

Precharge circuit에서 transistor의 size를 pmos : 120nm로 결정하였습니다.

Precharge circuit에서 transistor의 size를 위와 같이 결정한 이유는 다음과 같습니다.

1bit sram testbench에서 test 해본 결과 120nm에서 50ps동안 precharge를 해주었을 때, BL, BLB가 VDD까지 올라감을 확인할 수 있었습니다.

※ 하지만 이 결과는 1bit sram이였으며 parasitic extraction을 진행하지 않은 경우입니다. 추후 resizing of transistor 파트에서 resizing에 대해 다루도록 하겠습니다.

3. Row decoder

Row decoder에서 transistor의 size를 입력쪽의 INV의 size를 3x, NAND의 size를 2x, 출력쪽의 INV의 size를 5x로 결정하였습니다.

Row decoder에서 transistor의 size를 위와 같이 결정한 이유는 다음과 같습니다.

- 출력쪽의 INV의 size를 5x로 결정한 이유는 한 WL line 당 16개의 access transistor를 driving 해주어야 했기 때문입니다.

- NAND의 size를 2x로 결정한 이유는 출력쪽의 INV 5x를 driving해야 했기 때문입니다.

- 입력 쪽의 INV의 size를 3x로 결정한 이유는 INV 하나가 4개의 NAND를 driving해야 했기 때문입니다.

※ 하지만 이 결과는 parasitic extraction을 진행하지 않은 경우입니다. 추후 resizing of transistor 파트에서 resizing에 대해 다루도록 하겠습니다.

4. Column decoder

Column decoder에서 transistor의 size를 nmos : 700nm, pmos : 840nm, INV의 size를 3x로 결정하였습니다.

Column decoder에서 transistor의 size를 위와 같이 결정한 이유는 다음과 같습니다.

1bit sram testbench에서 column decoder없이 write driver만을 사용하여 쓰기 작업을 수행하였을 때, 쓰기 작업이 700nm에서 원활하게 됨을 확인하였기 때문에, 신호를 통과 시키는 logic인 column decoder는 크기를 write driver와 똑같이 맞춰주기 위해서 위와 같은 size를 결정하였습니다.

또한 Column decoder의 INV size를 3x로 결정한 이유는 nmos 8개 pmos 8개의 총 16개의 transistor를 driving 하여야 했기 때문입니다.

※ 하지만 이 결과는 parasitic extraction을 진행하지 않은 경우입니다. 추후 resizing of transistor 파트에서 resizing에 대해 다루도록 하겠습니다.

5. Sense amplifier

Sense amplifier에서 transistor의 size를 nmos : 120nm, pmos : 145nm, INV의 size를 3x로 결정하였습니다.

Sense amplifier에서 transistor의 size를 위와 같이 결정한 이유는 다음과 같습니다.

BL, BLB 쪽의 입력저항이 무한대이기 때문에 입력 쪽으로는 전류가 흐르지 않고, sense amp는 sense amp의 내부 전류만으로 동작할 수 있기 때문입니다.(동작이 어느정도 분리되어 있습니다.) 또한 BL, BLB line의 신호가 충분히 크기 때문에 transistor size가 최소가 되더라도 그 때의 gm값을 통해 신호를 충분히 증폭시킬 수 있을 것이라고 판단했습니다.

6. Write driver

Write driver에서 transistor의 size를 nmos : 700n, INV의 size를 2x로 결정하였습니다.

Write driver에서 transistor의 size를 위와 같이 결정한 이유는 다음과 같습니다.

1bit sram testbench에서 nmos가 700일 때 write 동작이 정상적으로 수행됨을 확인할 수 있었기 때문입니다.