Uni. Project/64bit Sram Design

64bit Sram Design (5) - Layout Design

Moamin

2022. 7. 14. 23:09

64bit sram design 프로젝트에서 각각의 sub-block의 layout과 전체 design의 schematic과 layout은 다음과 같습니다.

1. Layout of Sram cell

6T sram의 layout은 다음과 같습니다.

2. Layout of Precharge circuit

precharge cell의 layout은 다음과 같습니다.

DRC에서 soft_check error가 발생한 이유는 precharge cell에 VSS가 없기 때문입니다. 추후에 cell을 통합하여 64bit sram을 만들었을 때에는 DRC가 문제없이 통과되는 것을 확인하였습니다.

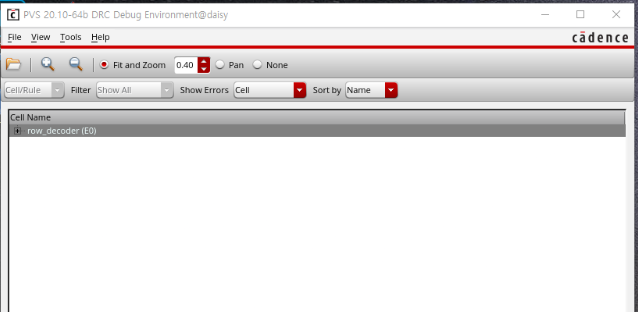

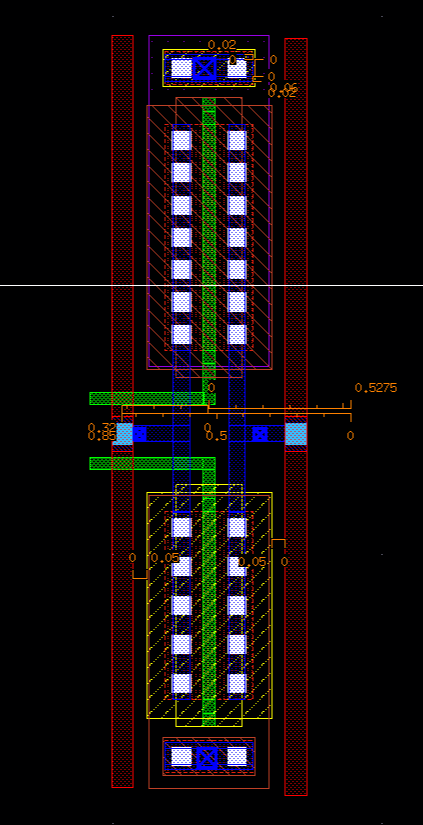

3. Layout of Row decoder

row decoder의 layout은 다음과 같습니다.

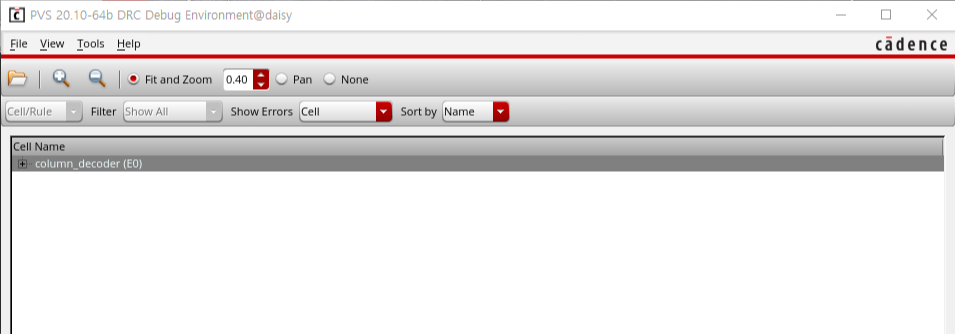

4. Layout of Column decoder

column decoder의 layout은 다음과 같습니다.

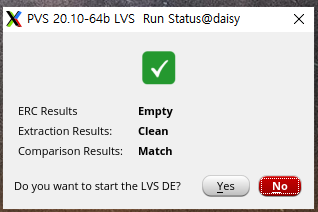

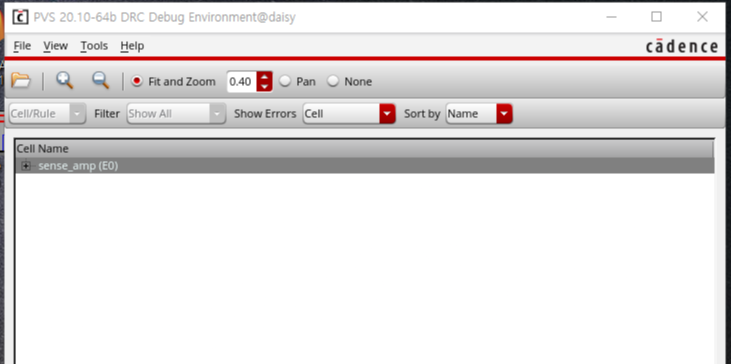

5. Layout of Sense amplifier

sense amplifier의 layout은 다음과 같습니다.

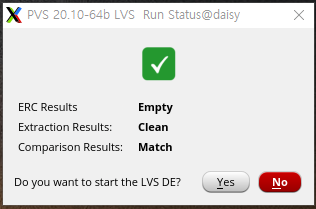

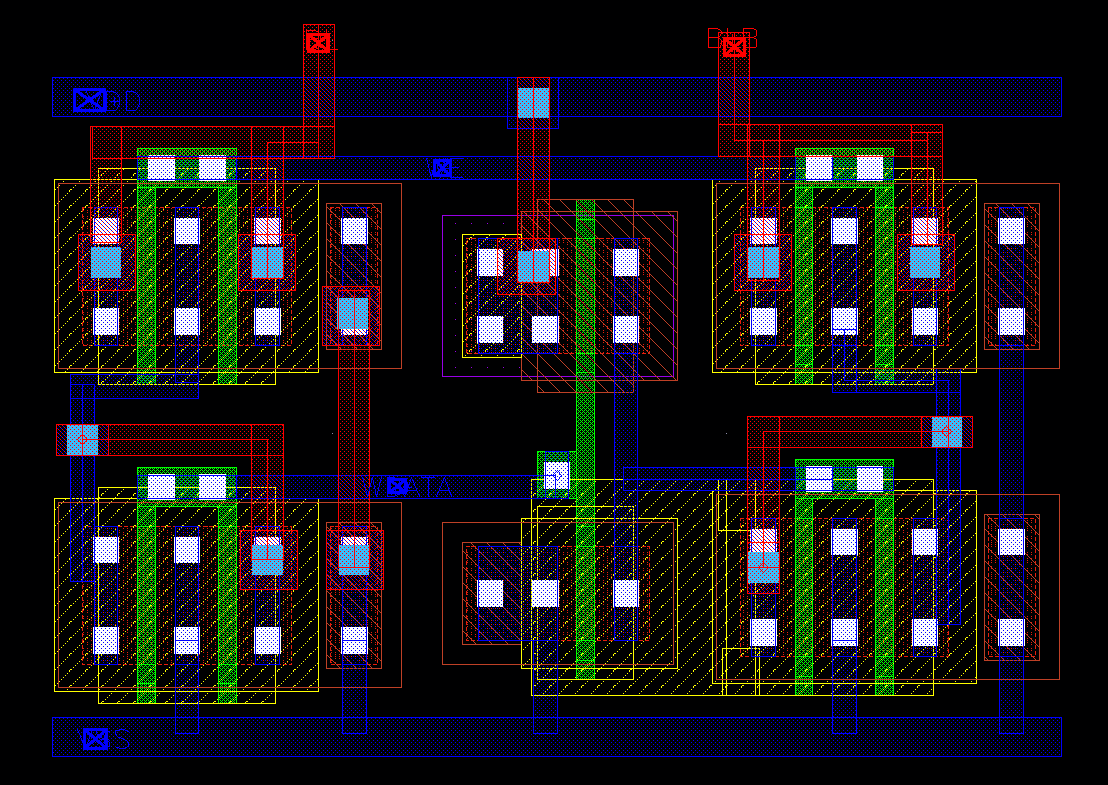

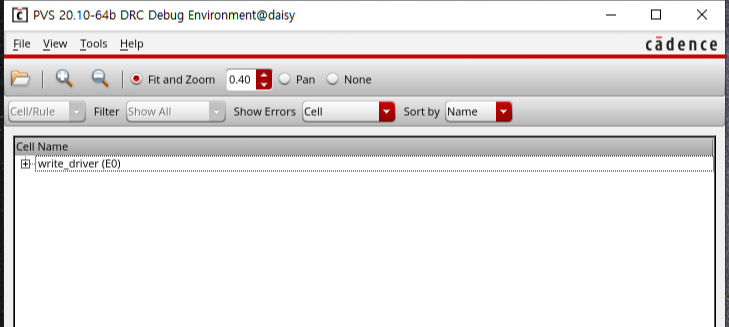

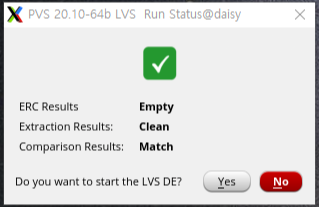

6. Layout of Write driver

write driver의 layout은 다음과 같습니다.

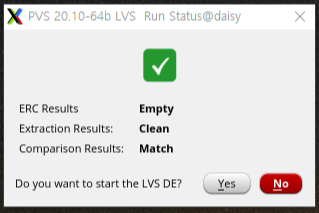

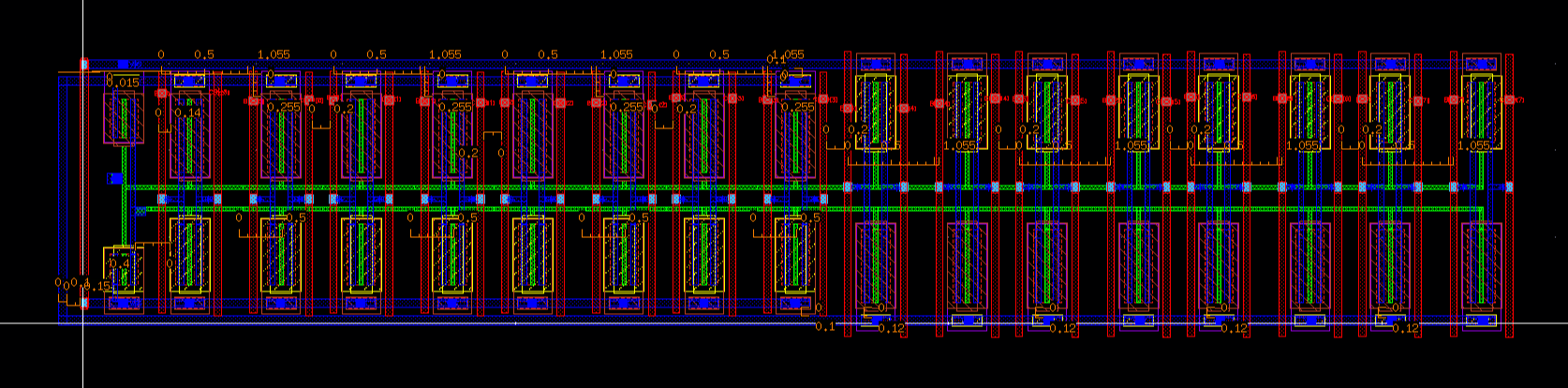

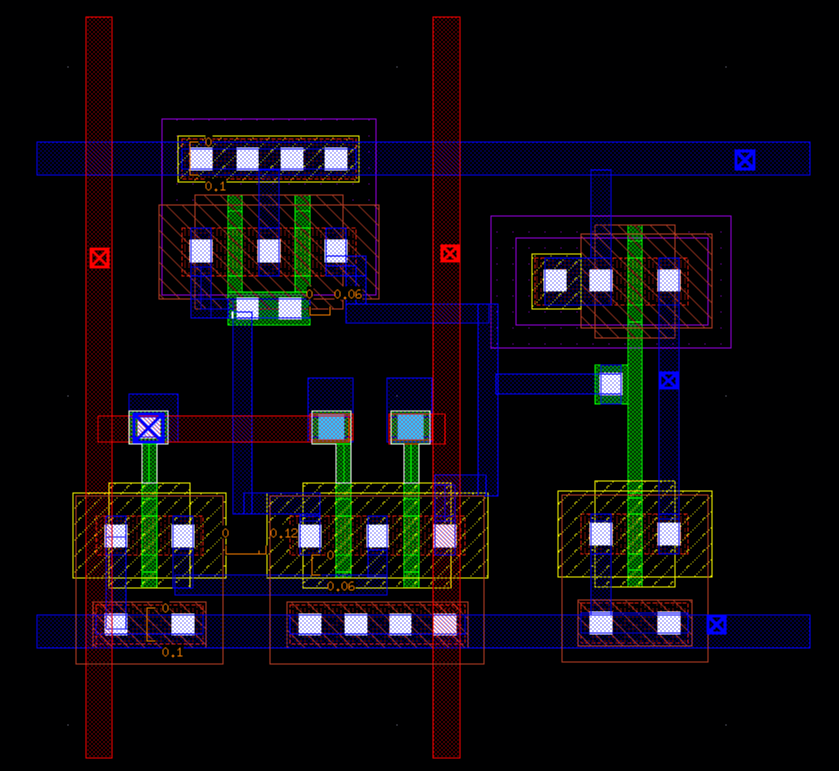

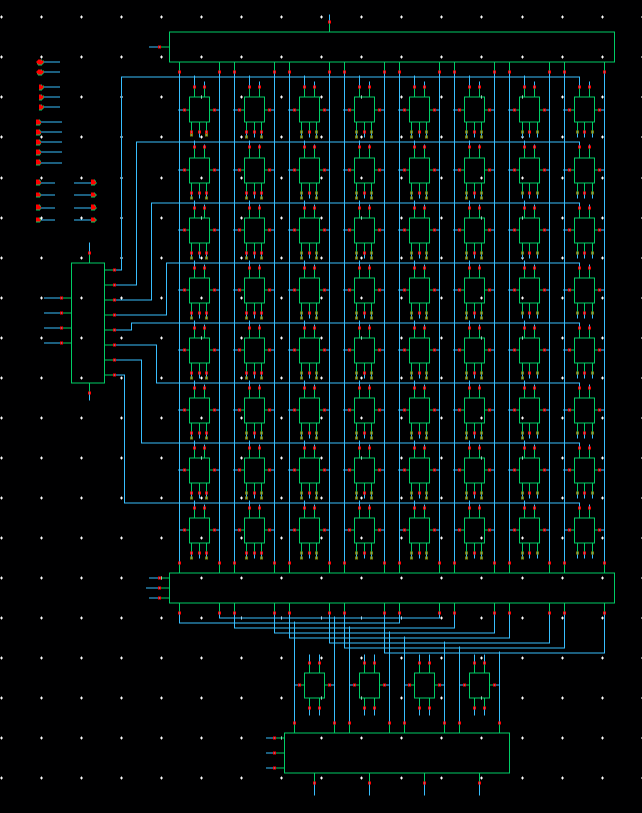

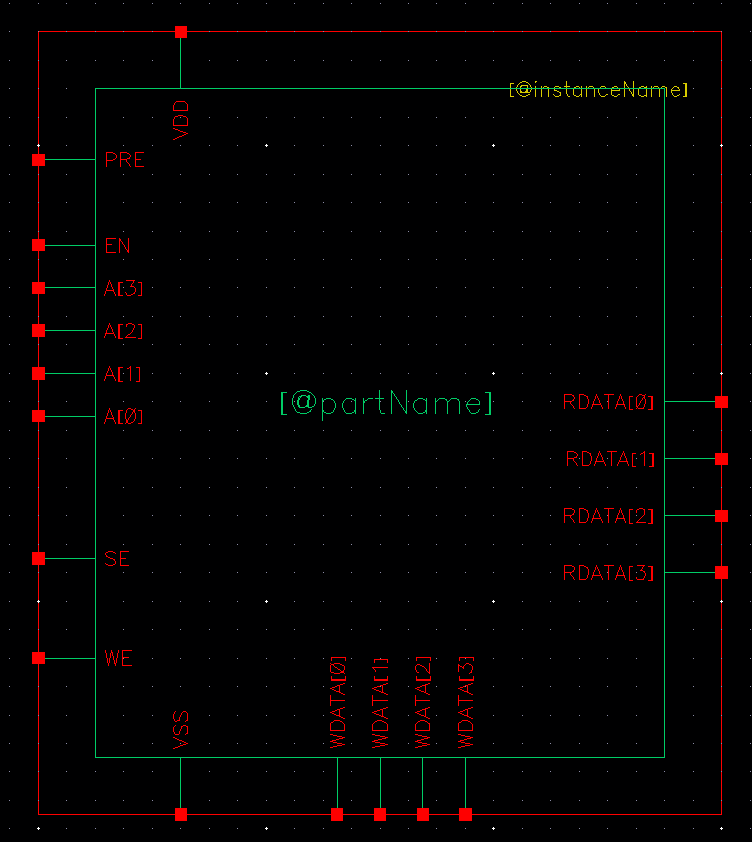

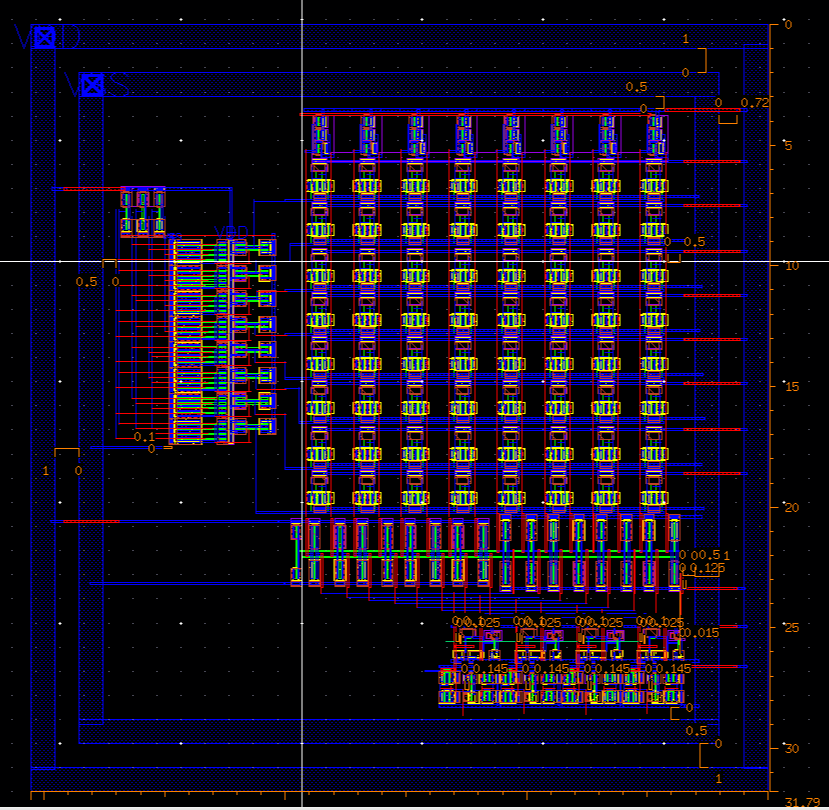

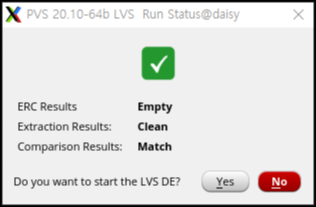

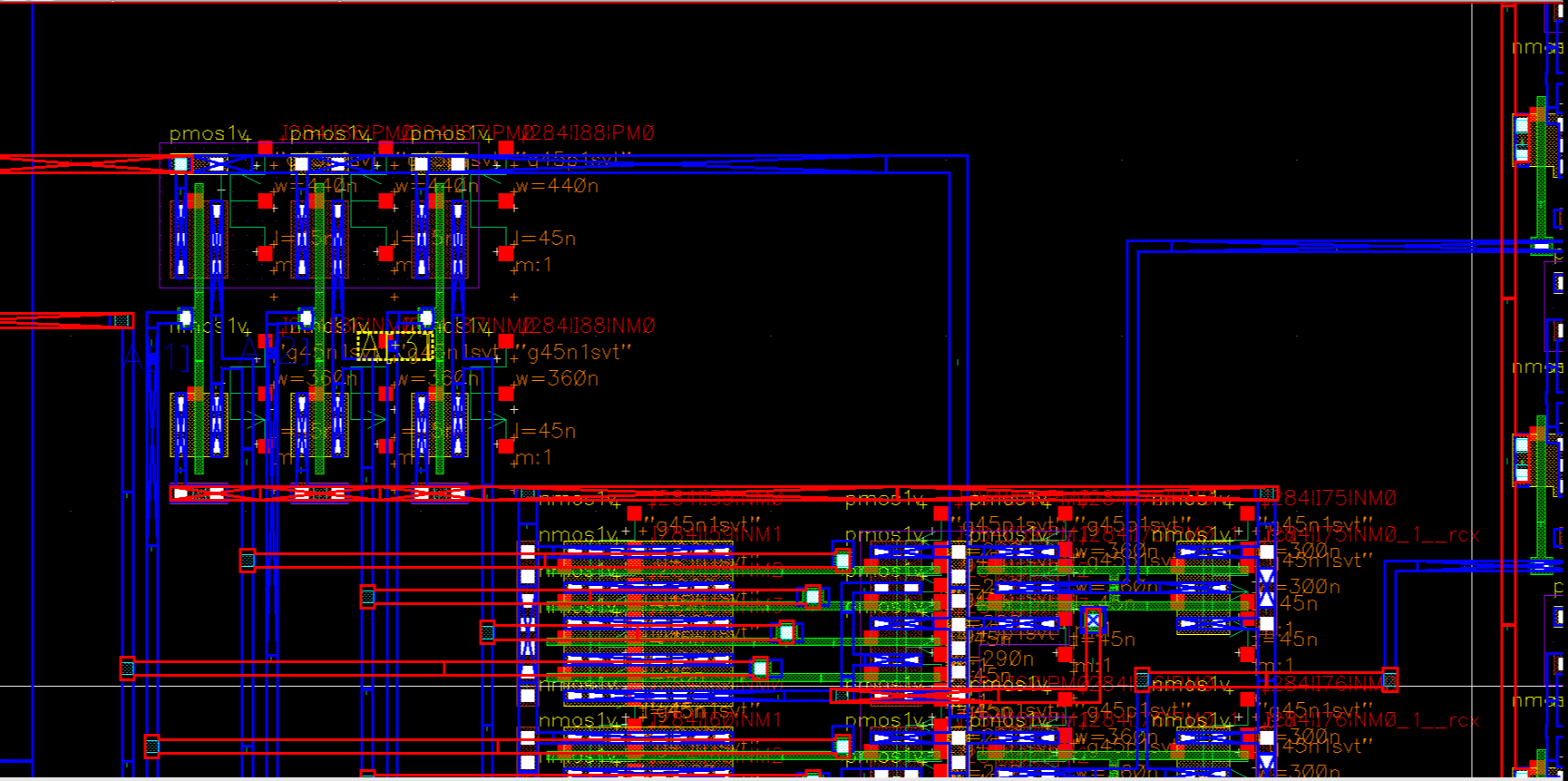

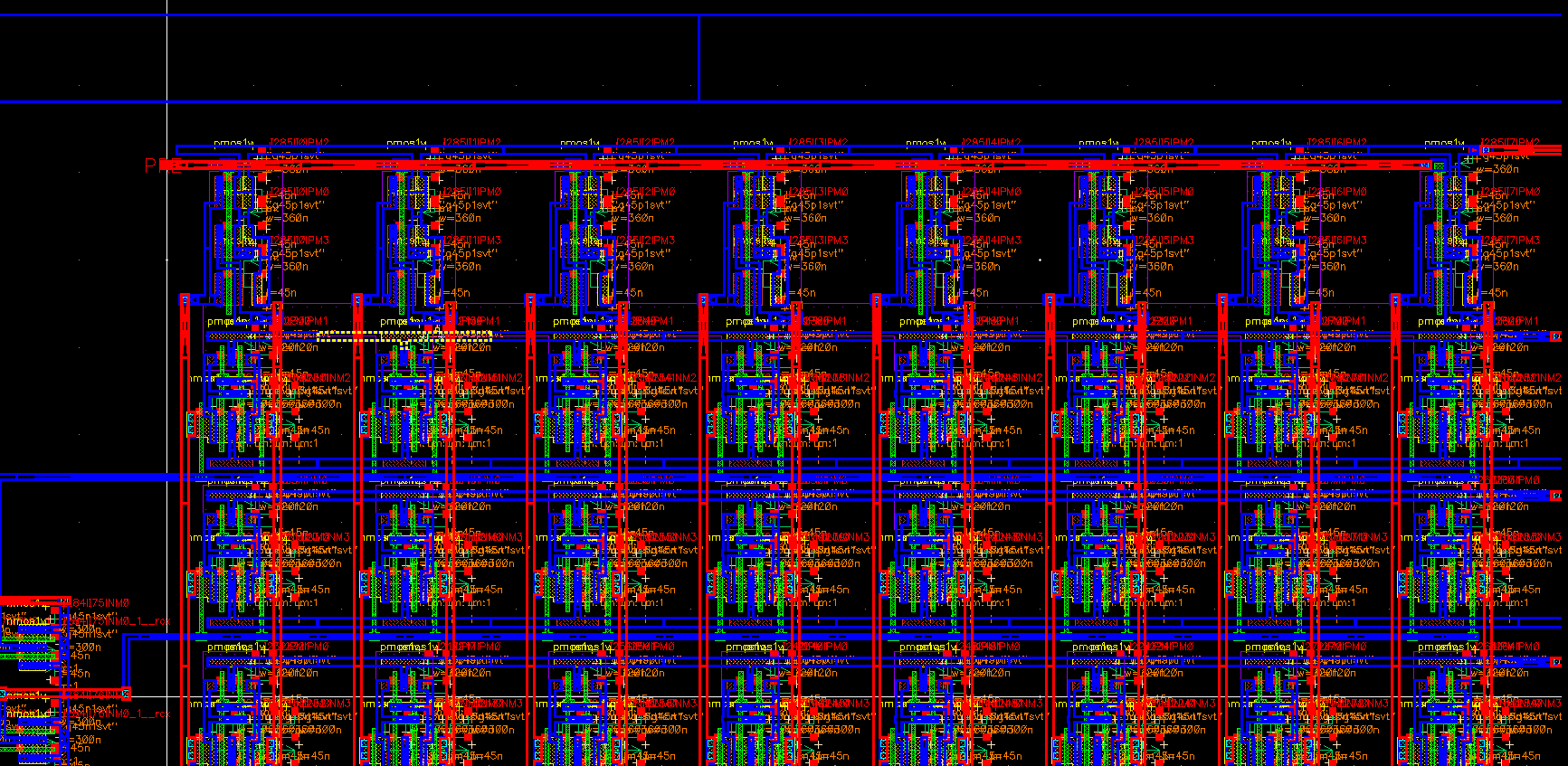

7. 64bit sram schematic & layout

64bit sram 의 schematic과 layout은 다음과 같습니다.

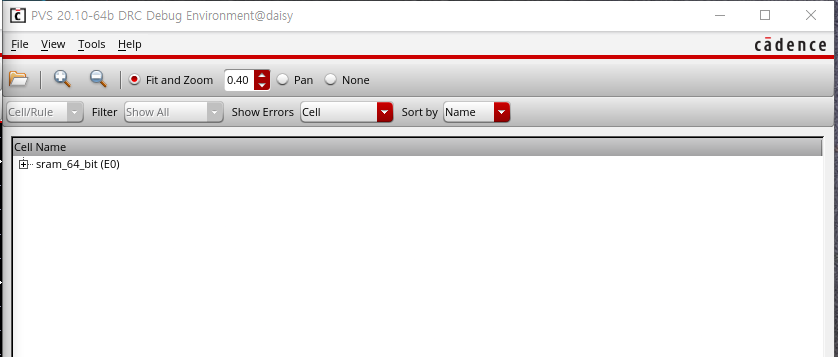

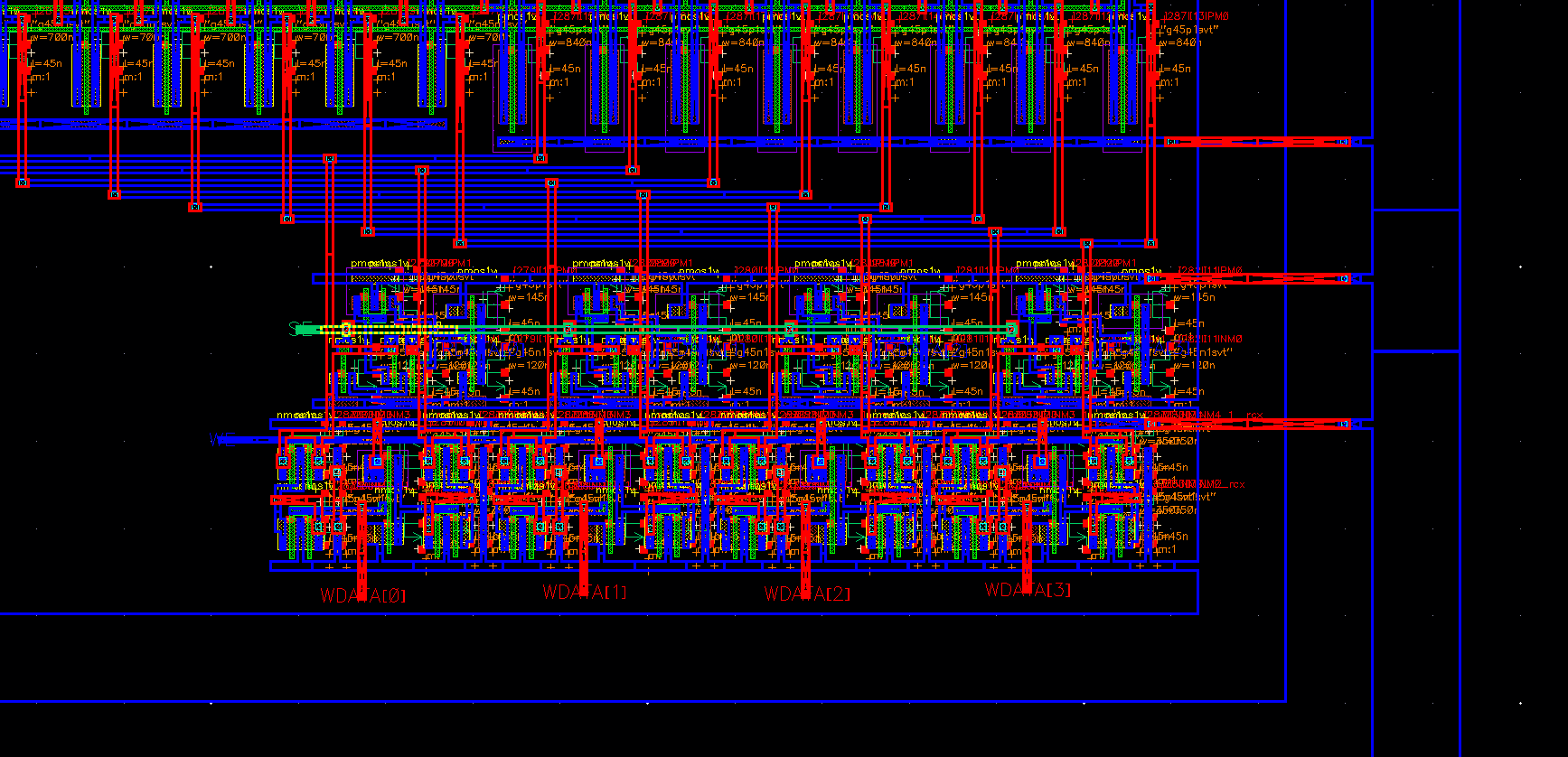

8. Parastic Extraction

64bit sram layout에서 Quantus를 통해 기생 성분을 추출한 결과는 다음과 같습니다.

위와 같이 layout에서 여러 기생성분들이 추출되는 것을 확인할 수 있었습니다.

반응형