64bit Sram Design (6) - Simulation & Post-layout simulation

64bit sram design 프로젝트에서 전체 64bit sram의 schematic simulation 결과와 layout에서 parasitic 값을 뽑아낸 후 post-layout simulation을 한 결과는 다음과 같습니다.

1. Schematic simulation result

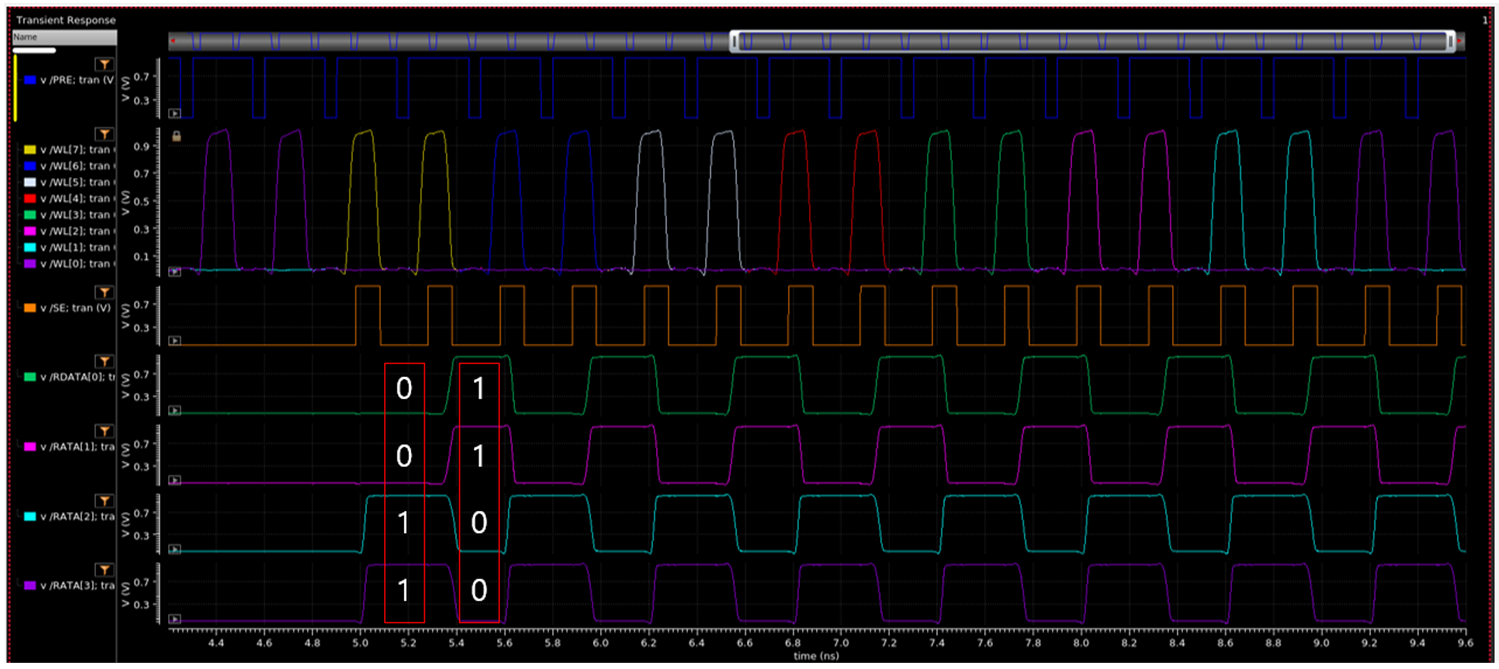

layout에서 기생성분을 추출하지 않은 체, schematic에서 system spec을 약 3.3GHz 맞추었을 때의

쓰기 동작 시뮬레이션 결과는 다음과 같습니다.

sram cell의 왼쪽 8*4개의 cell에는 0011을, sram cell의 오른쪽 8*4개의 cell에는 1100을 써 주었고 정상적으로 쓰기 동작이 됨을 확인할 수 있었습니다.

읽기 동작 시뮬레이션 결과는 다음과 같습니다.

위에서 쓴 값이 읽기 동작에서 정상적으로 읽힘을 확인할 수 있었습니다.

2. Post-layout simulation

결론부터 말하자면, post-layout simulation에서는 읽고 쓰기 동작이 정상적으로 수행되지 못했습니다.

그원인을 분석한 결과 다음과 같은 시뮬레이션 결과를 확인할 수 있었습니다.

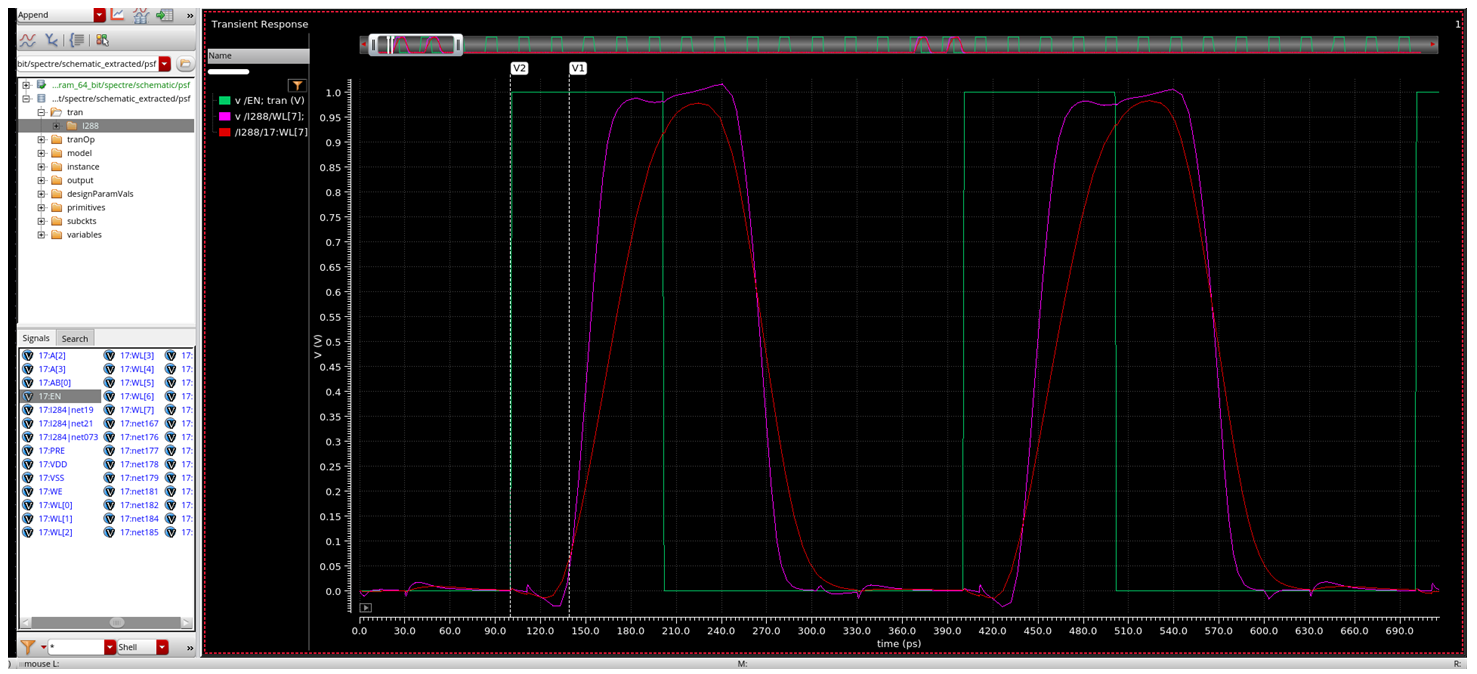

post-layout simulation에서 system spec을 약 3.3GHz 맞추었을 때 시뮬레이션을 돌린 결과

기생성분으로 인해 WL[x] 신호가 원하는 범위만큼 나오지 않음을 확인할 수 있었습니다.

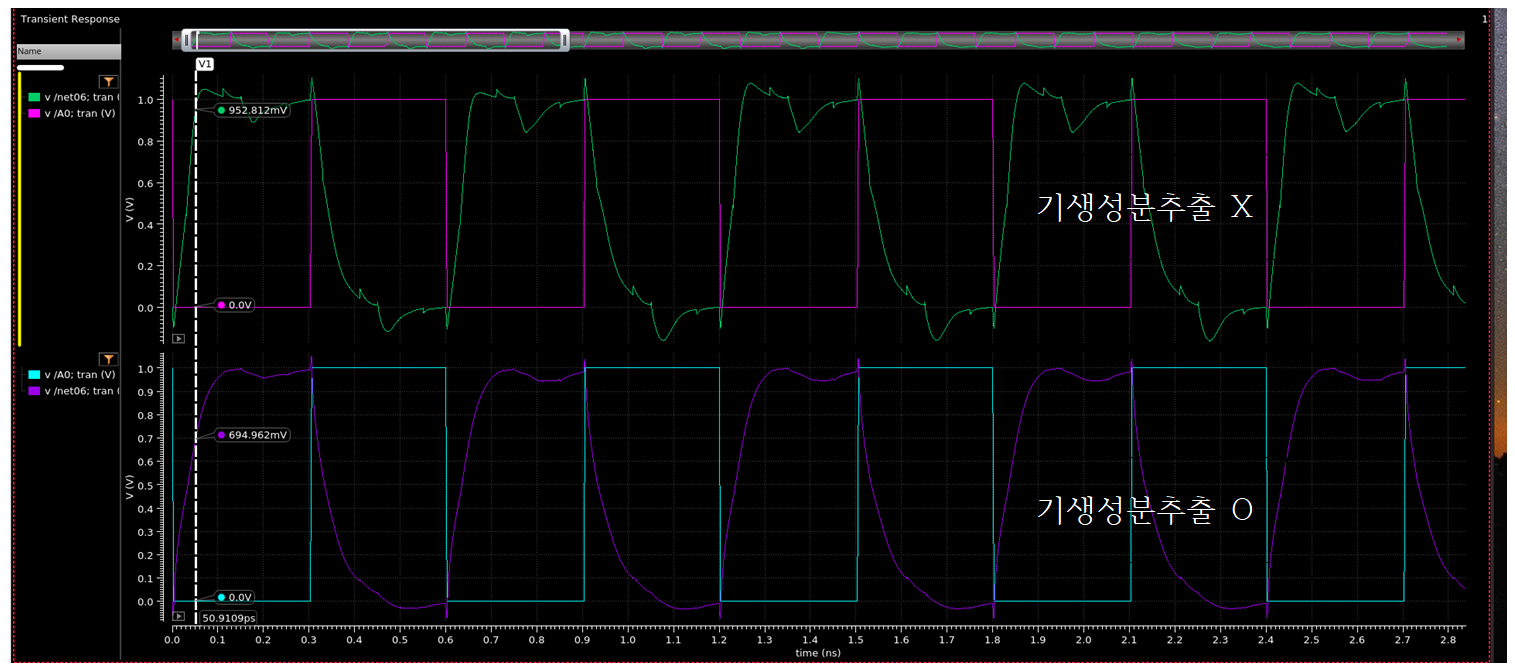

기생성분으로 인해 column decoder의 인버터를 통과한 후의 신호인 AB[0] 신호의 delay가 생각보다 매우 큼을 확인할 수 있었습니다.

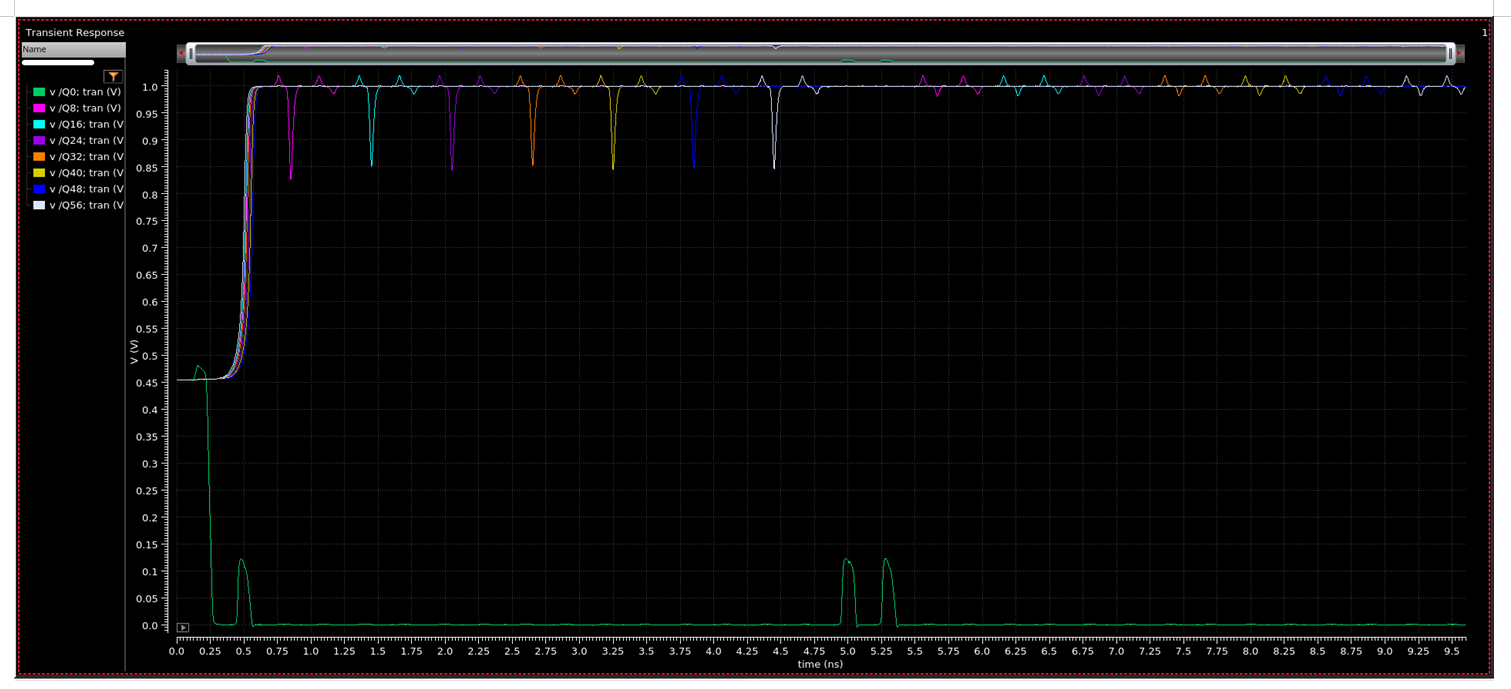

기생성분들로 인해 sram cell에 write 동작이 원활하게 되지 않음을 확인할 수 있었습니다.

결과적으로 기생성분들로 인해 64bit sram의 동작이 제대로 수행되지 않았습니다. 위와 같은 문제를 해결하기 위해서 특정 sub-block의 transistor size를 재조정 해주었습니다. 이에 대해서는 다음 글에서 다루도록 하겠습니다.