64bit Sram Design (7) - Resizing of transistor & Spec downgrade

1. Resizing of transistor

앞서 기생성분들로 인해 64bit sram의 동작이 제대로 수행되지 않았음을 언급하였습니다. 따라서 앞선 문제들을 해결하기 위해서 특정 sub-block의 transistor size를 재조정 해주었습니다.

(1). Resizing of precharge circuit

앞서 transistor sizing 파트에서 Precharge cell이 pmos : 120nm 일 때 64bit testbench에서 Precharge가 정상적으로 되지 않음을 언급하였습니다. 따라서 저희는 pmos를 360nm로 바꾸어 주었습니다.

아래의 시뮬레이션 결과는 precharge를 비교한 결과입니다.

pmos를 360nm로 했을 때, 확실히 precharge의 결과가 더 좋아짐을 확인하였습니다.

precharge cell의 layout 또한 다시 그려주었습니다.

(2). Resizing of row decoder

앞서 transistor sizing 파트에서 Row decoder의 WL 신호가 기생 커패시터로 인해 원하는 범위안에 들어오지 않음을 언급하였습니다.

먼저 기생 커패시터 성분이 얼마나 되는지 알아야 했습니다. 그래서 기생성분을 추출하지 않고 시뮬레이션을 돌렸을 때, 얼마만큼의 load cap을 달아주어야 기생성분을 추출한 것과 파형이 비슷하게 나오는지 확인하였습니다. 그 결과 load cap이 8f F 일 때, 기생 커패시터가 있는 파형과 비슷하게 나옴을 확인하였습니다.

이 결과를 토대로 8fF의 load cap이 있을 때, 원래 정상적으로 깨끗하게 나오던 신호와 같은 신호를 뽑아주기 위해서 sizing을 반복하여 시뮬레이션을 돌린 결과 다음과 같은 결과를 얻을 수 있었습니다.

input INV의 size : x16, nand4의 size : x6, output INV의 size : x22일 때 면적 대비 좋은 신호결과를 얻을 수 있었습니다.

row decoder의 layout 또한 다시 그려주었습니다.

(3). Resizing of column decoder

앞서 sizing reason 파트에서 Column decoder의 INV delay가 생각보다 크게 나옴을 언급하였습니다.

INV size를 재조정한 뒤 시뮬레이션하여 다음과 같은 결과를 확인하였습니다.

시뮬레이션 결과 column decoder의 INV의 size를 x10로 재조정 하였습니다.

(4). Resizing of 64bit sram

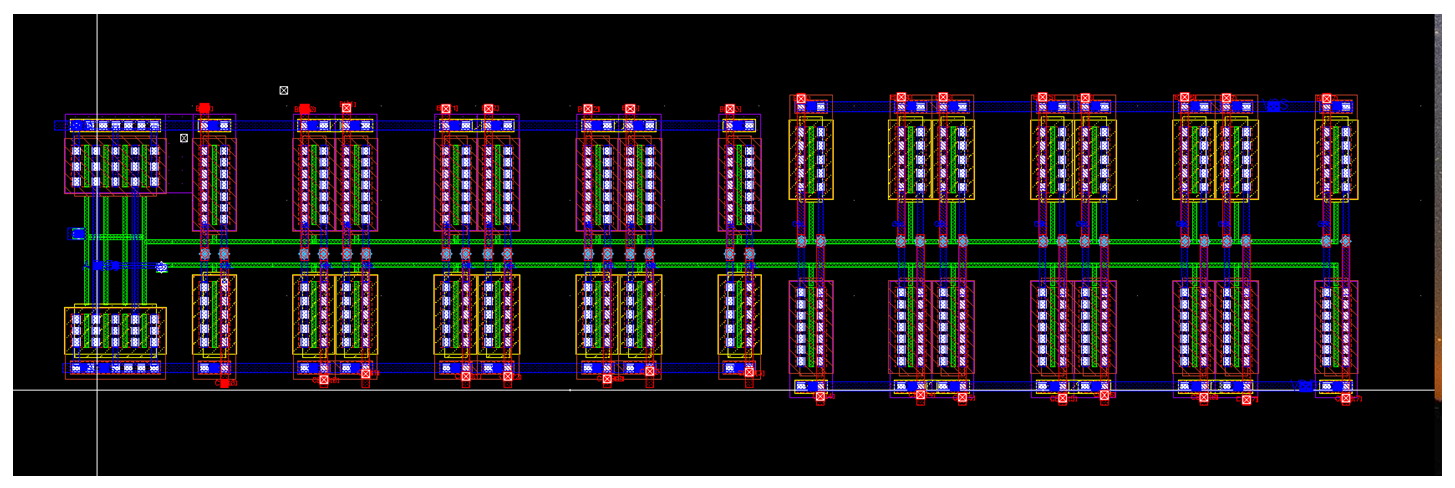

위의 sub-block들을 바꾸었기 때문에 64bit sram 또한 다시 layout을 그려주었습니다.

다음은 다시 그려준 64bit sram의 layout입니다.

2. Spec downgrade

sizing을 조정해주었지만 sram cell에서 write 동작이 제대로 수행되지 않았습니다.

write driver와 precharge circuit을 resizing 할 수 도 있었습니다. 하지만 위의 cell들을 다시 resizing하고 시뮬레이션을 돌려보기에는 프로젝트의 시간이 부족할 것 같았기 때문에 저희는 system spec을 낮추었습니다.

낮춘 system spec은 다음과 같습니다.

0.4ns 이내에 하나의 읽기 또는 쓰기 동작이 완료되도록 한다.

즉 sram frequency는 2.5GHz가 되도록 한다.

따라서 위의 specification에 따라 각 동작에서의 신호의 pulse width를 정해주었습니다.

다음은 downgrade한 쓰기 동작의 system spec입니다.

PRE 신호의 pulse width는 100ps, WL[x], WEN 신호의 pulse width는 200ps이고 각 신호 사이의 간격은 50ps로 설정하였습니다.

다음은 downgrade한 읽기 동작의 system spec입니다.

PRE 신호의 pulse width는 100ps, WL[x], SAE 신호의 pulse width는 200ps이고 각 신호 사이의 간격은 50ps로 설정하였습니다.

이렇게 spec을 낮춘 결과, 시뮬레이션 결과가 원했던 방식으로 잘 수행됨을 확인할 수 있었습니다. 이에 대해서는 다음 글에서 다루도록 하겠습니다.