64bit sram design의 목표는 다음과 같다.

각각의 sram cell에 자신의 주소값을 쓰고 읽는 것이 본 프로젝트의 목표이다.

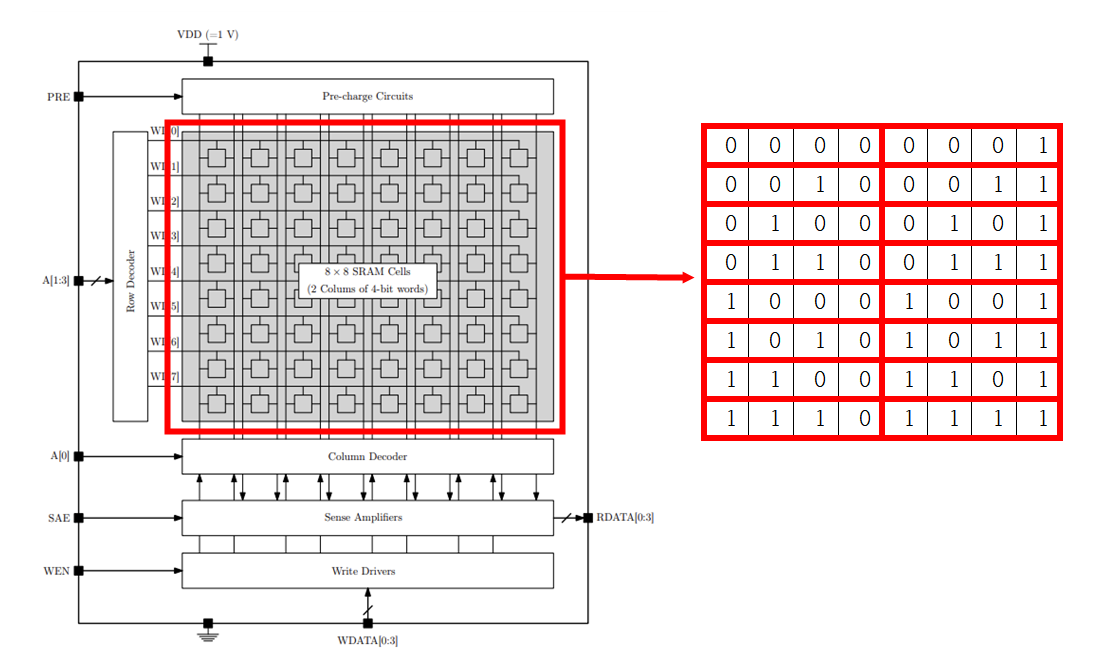

64bit sram의 block diagram은 다음과 같다.

64bit sram의 정상적인 동작을 위해 필요한 회로는 다음과 같다.

1. Sram cell

2. Precharge circuit

3. Row decoder

4. Column decoder

5. Sense amplifier

6. Write driver

각각의 회로에 대한 역할은 다음과 같다.

1. Sram cell

읽기 동작 - 읽기 동작 시, sram cell에서 저장된 정보를 읽는다.

쓰기 동작 - 쓰기 동작 시, sram cell에 원하는 정보를 쓴다.

Hold 동작 - Hold 동작 시, sram cell은 저장된 정보를 유지한다.

2. Precharge circuit

sram cell과 연결되어 있는 BL, BLB를 VDD로 precharge 시킨다.

3. Row decoder

A[1:3] 신호에 따라 WL[X] (X ∈ {0, 1, 2, 3, 4, 5, 6, 7})을 High로 만들고, 어떤 sram cell의 행(row)이 선택될 지를 결정한다.

4. Column decoder

A[0] 신호에 어떤 sram cell의 열(column)이 선택될 지를 결정한다.

5. Sense amplifier

read동작 시, BL, BLB line으로 읽어들인 sram cell의 data는 확실한 High, Low 신호가 아닌, degraded된 신호이기 때문에 이를 판단하는 것은 쉽지 않다. 그렇기 때문에 BL, BLB line의 전압차를 증폭하여 명확한 신호의 구분을 가능하도록 하는 역할을 한다.

6. Write driver

write동작 시, BL, BLB line을 통해 sram cell에 data를 쓰는 역할을 한다.

'Uni. Project > 64bit Sram Design' 카테고리의 다른 글

| 64bit Sram Design (6) - Simulation & Post-layout simulation (0) | 2022.08.02 |

|---|---|

| 64bit Sram Design (5) - Layout Design (0) | 2022.07.14 |

| 64bit Sram Design (4) - Transistor Sizing (1) | 2022.07.13 |

| 64bit Sram Design (3) - Circuit Topology & Schematic Design (1) | 2022.07.11 |

| 64bit Sram Design (2) - System Specification (0) | 2022.07.10 |