64bit sram design 프로젝트에서 우리 팀이 정한 system spec은 다음과 같다.

0.3ns 이내에 하나의 읽기 또는 쓰기 동작이 완료되어야 한다.

위의 spec을 만족시켜주기 위해서 우리 팀이 정한 sub-block specification은 다음과 같다.

Sub-Block Specification

1. Sram cell

hold 동작 - WL[X]에 0의 값이 인가된 동안에는 sram cell에 저장된 정보가 정상적으로 유지되어야 한다.

Write 동작

- Sram에 저장된 정보가 바뀌지 않도록 해야한다.

- WL[X]와 WEN(write enable) 신호가 가해지는 100ps 동안 값을 정상적으로 바꿀 수 있어야 한다.

Read 동작 - WL[X]와 SAE(sense amplifier enable) 신호가 가해지는 100ps 동안 precharge된 BL, BLB line의 값을 sense ampifier가 감지할 수 있을 정도로 바꿀 수 있어야 한다.

2. Precharge circuit

PRE 신호가 50ps 동안 가해지면, 그 시간 안에 BL, BLB line을 VDD로 charge 시켜주어야 한다.

※ 왜 VSS가 아닌 VDD로 precharge 시키는가?

sram cell의 access transistor가 nmos이기 때문에, nmos는 0의 신호는 잘 전달하는 반면, 1의 신호는 degraded 되어 전달된다. 그렇기 때문에 BL, BLB line을 VDD로 precharge하여 nmos가 1의 신호를 잘 전달하지 못하는 것을 보상한다.

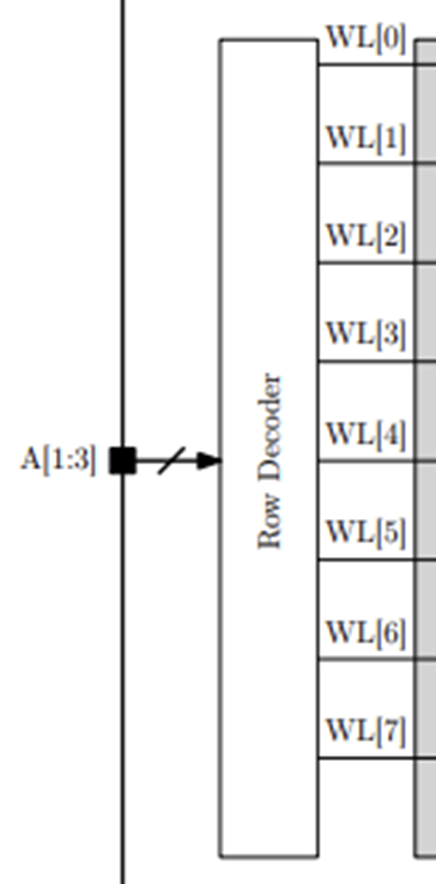

3. Row decoder

Input signal : A[1], A[2], A[3], EN(Enable)

Output signal : WL[X], X = 0, 1, 2, 3, 4, 5, 6, 7

A[1], A[2], A[3]의 값에 따라 EN 신호가 high일 때만 WL[X]에서 신호를 출력한다. 따라서 EN 신호가 100ps 만큼 가해지면, WL[X] 신호를 100ps 동안 high로 만들어주어야 한다.

※ 왜 EN(Enable) signal이 필요한가?

EN(Enable) 신호를 사용하지 않고 row decoder를 구성할 경우 8개의 WL[x]중 무조건 1개의 WL[X]가 켜진다.

이는 sram cell의 의도치 않은 쓰기 혹은 읽기 동작을 유발할 수 있다. 또한 파워 소모면에서도 손해를 입는다.

4. Colunm decoder

Column decoder는 transmission gate 16개로 구성된다.

A[0], AB[0] 신호에 따라 상위 8개의 transmisson gate가 열리거나 닫히고, 하위 8개의 transmission gate가 닫히거나 열리게 된다.

AB[0]는 A[0]가 인버터를 통과한 후의 신호이다. 따라서 AB[0]의 delay를 최대한 작게 하는 것이 중요하다.

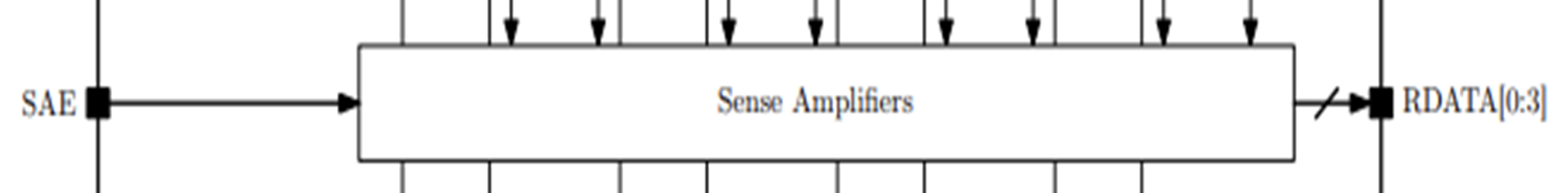

5. Sense ampifier

SAE 신호가 가해졌을 때, BL, BLB의 전압차이를 더욱 크게 증폭하여 현재 데이터를 읽어낸다.

SAE 신호가 100ps 동한 가해질 때, Sram cell의 값을 정상적으로 읽어내는 것이 중요하다.

6. Write driver

WEN 신호가 100ps 동안 가해지면, write driver와 연결된 BL, BLB line에 WDATA의 값에 따라 각각 (0, 1) 또는 (1, 0) 이라는 값이 쓰인다.

WEN 신호가 100ps 동안 가해질 때, Sram cell에 정상적으로 값을 쓰는 것이 중요하다.

'Uni. Project > 64bit Sram Design' 카테고리의 다른 글

| 64bit Sram Design (6) - Simulation & Post-layout simulation (0) | 2022.08.02 |

|---|---|

| 64bit Sram Design (5) - Layout Design (0) | 2022.07.14 |

| 64bit Sram Design (4) - Transistor Sizing (1) | 2022.07.13 |

| 64bit Sram Design (3) - Circuit Topology & Schematic Design (1) | 2022.07.11 |

| 64bit Sram Design (1) - Project Objective (0) | 2022.07.10 |